www.ti.com

EMIF

The DDR2/3/mDDR memory controller starts servicing new memory accesses after Refresh Release level

is cleared. If any of the commands in the Command FIFO have class of service latency counters that are

expired, the DDR2/3/mDDR memory controller will not wait for Refresh Release level to be cleared but will

only perform one refresh command and exit the refresh state.

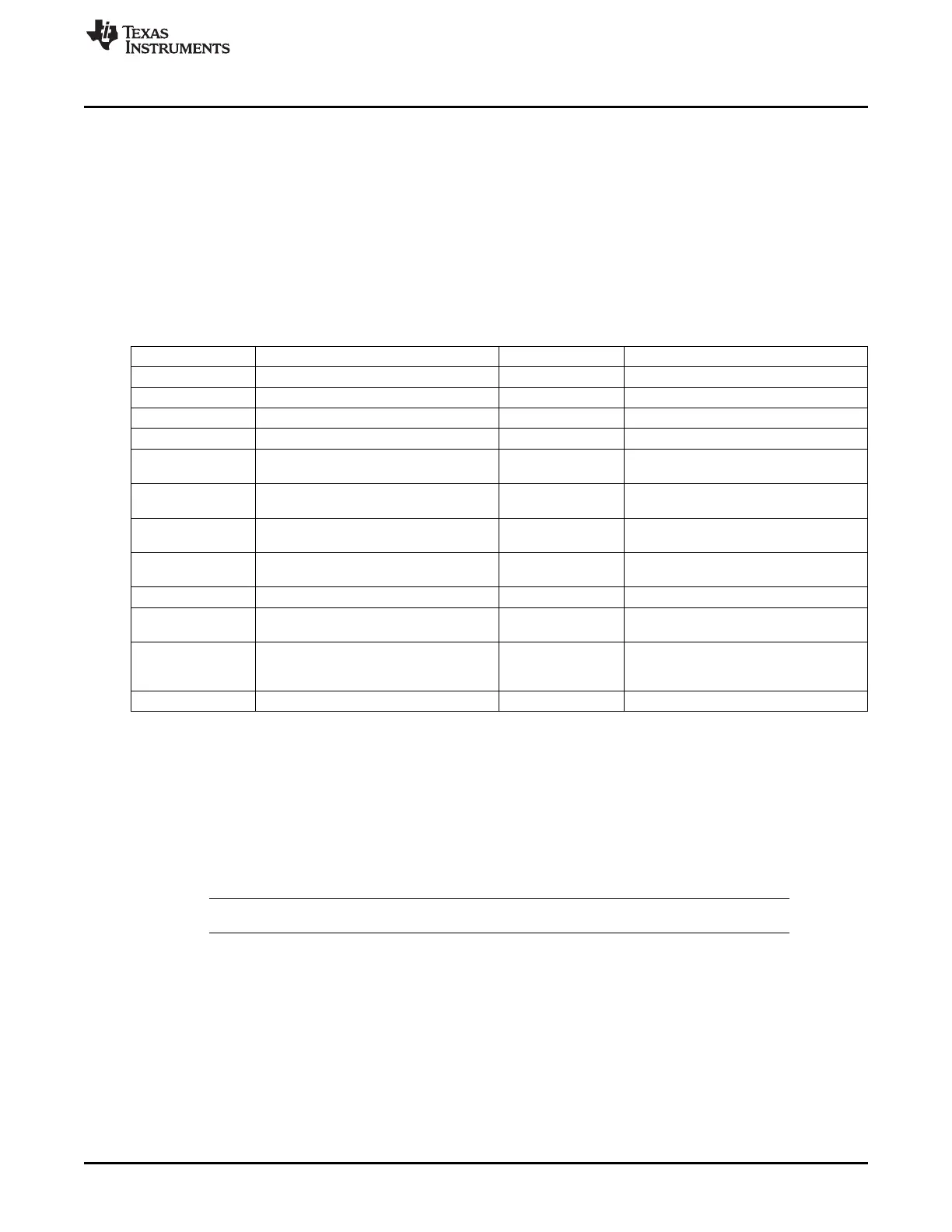

7.3.3.5.6 Performance Counter Configuration

Table 7-109 shows the possible filter configurations for the two performance counters (REG_CNTR1_CFG

and REG_CNTR2_CFG). These filter configurations can be used in conjunction with an OCP connection

ID and/or an external chip select to obtain performance statistics for a particular OCP master and/or an

external chip select.

Table 7-109. Filter Configurations for Performance Counters

cntrN_cfg

(1)

cntrN_region_en cntrN_mconnid_en Description

0x0 0x0 0x0 or 0x1 Count total SDRAM accesses.

0x1 0x0 0x0 or 0x1 Count total SDRAM activations.

0x2 0x0 or 0x1 0x0 or 0x1 Count total reads.

0x3 0x0 or 0x1 0x0 or 0x1 Count total writes.

Count number of DDR clock cycles OCP

0x4 0x0 0x0

Command FIFO is full.

Count number of DDR clock cycles OCP

0x5 0x0 0x0

Write Data FIFO is full.

Count number of DDR clock cycles OCP

0x6 0x0 0x0

Read Data FIFO is full.

Count number of DDR clock cycles OCP

0x7 0x0 0x0

Return Command FIFO is full.

0x8 0x0 or 0x1 0x0 or 0x1 Count number of priority elevations.

Count number of DDR clock cycles that a

0x9 0x0 0x0

command was pending.

Count number of DDR clock cycles for

0xA 0x0 0x0 which the memory data bus was

transferring data.

0xB - 0xF 0x0 0x0 Reserved for future use.

(1)

When MReqDebug is set to a 1 for a particular OCP command, the performance counters will not be incremented for that

particular command if the cntrN_cfg values are equal to 0x0, 0x1, 0x2, 0x3, or 0xA.

7.3.3.6 DDR3 Read-Write Leveling

The DDR2/3/mDDR memory controller supports read-write leveling in conjunction with the DDR PHY. The

DDR2/3/mDDR memory controller supports two types of write/read leveling:

1. Full leveling

2. Incremental leveling

NOTE: Please refer the device specific data sheet to know the type of leveling supported.

Each leveling type has three parts:

1. Write leveling

2. Read DQS gate training

3. Read data eye training

Read and write leveling is only supported to DDR3 memory.

417

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...