www.ti.com

Integration

12.2.2 TSC_ADC Clock and Reset Management

The TSC_ADC has two clock domains. The ADC uses the adc_clk. The bus interfaces, FIFOs, sequencer,

and all other lofic use the ocp_clk.

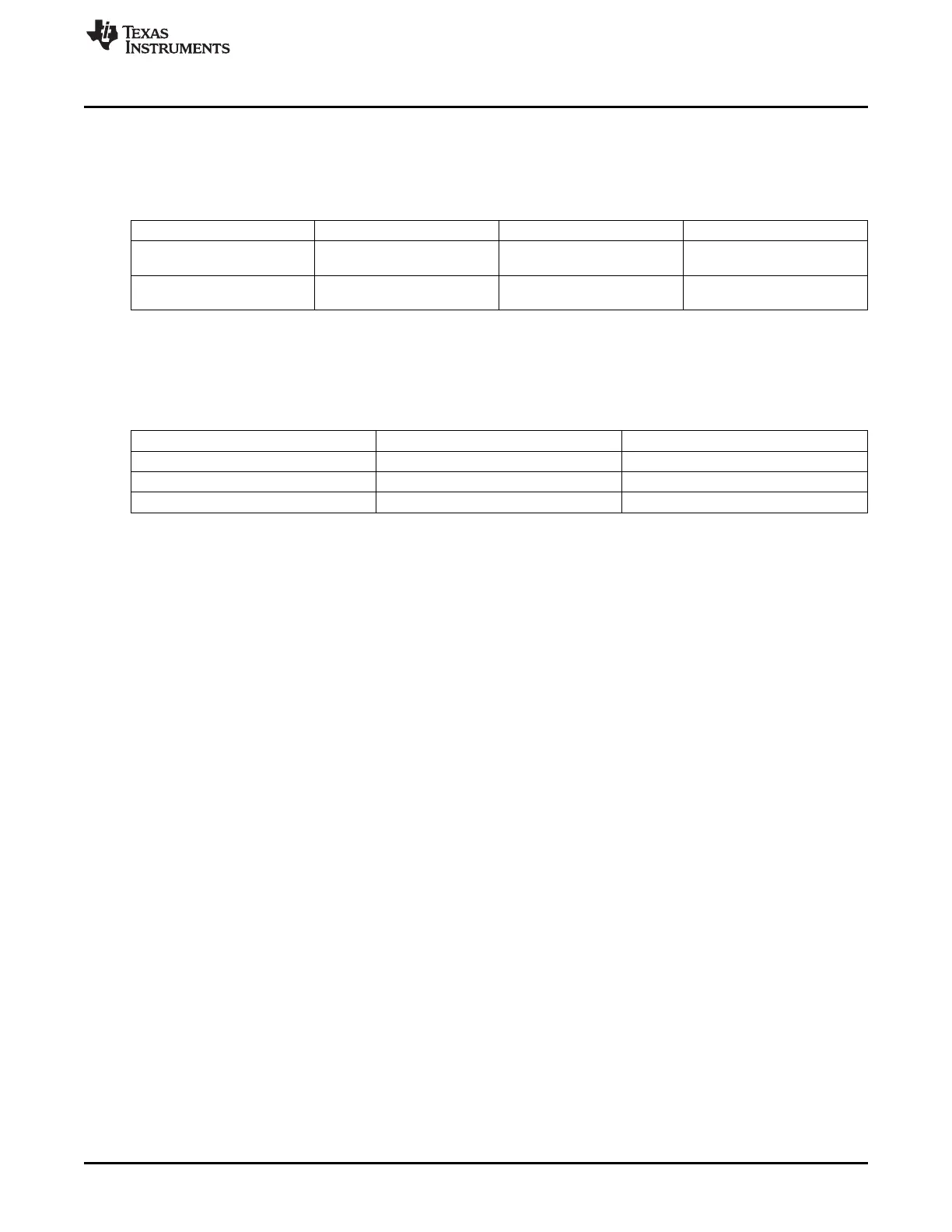

Table 12-2. TSC_ADC Clock Signals

Clock Signal Max Freq Reference / Source Comments

ocp_clk 100 MHz CORE_CLKOUTM4 / 2 pd_pwkup_l4_wkup_gclk

OCP / Functional clock From PRCM

adc_clk 24 MHz CLK_M_OSC pd_wkup_adc_fclk

ADC clock (typ) From PRCM

12.2.3 TSC_ADC Pin List

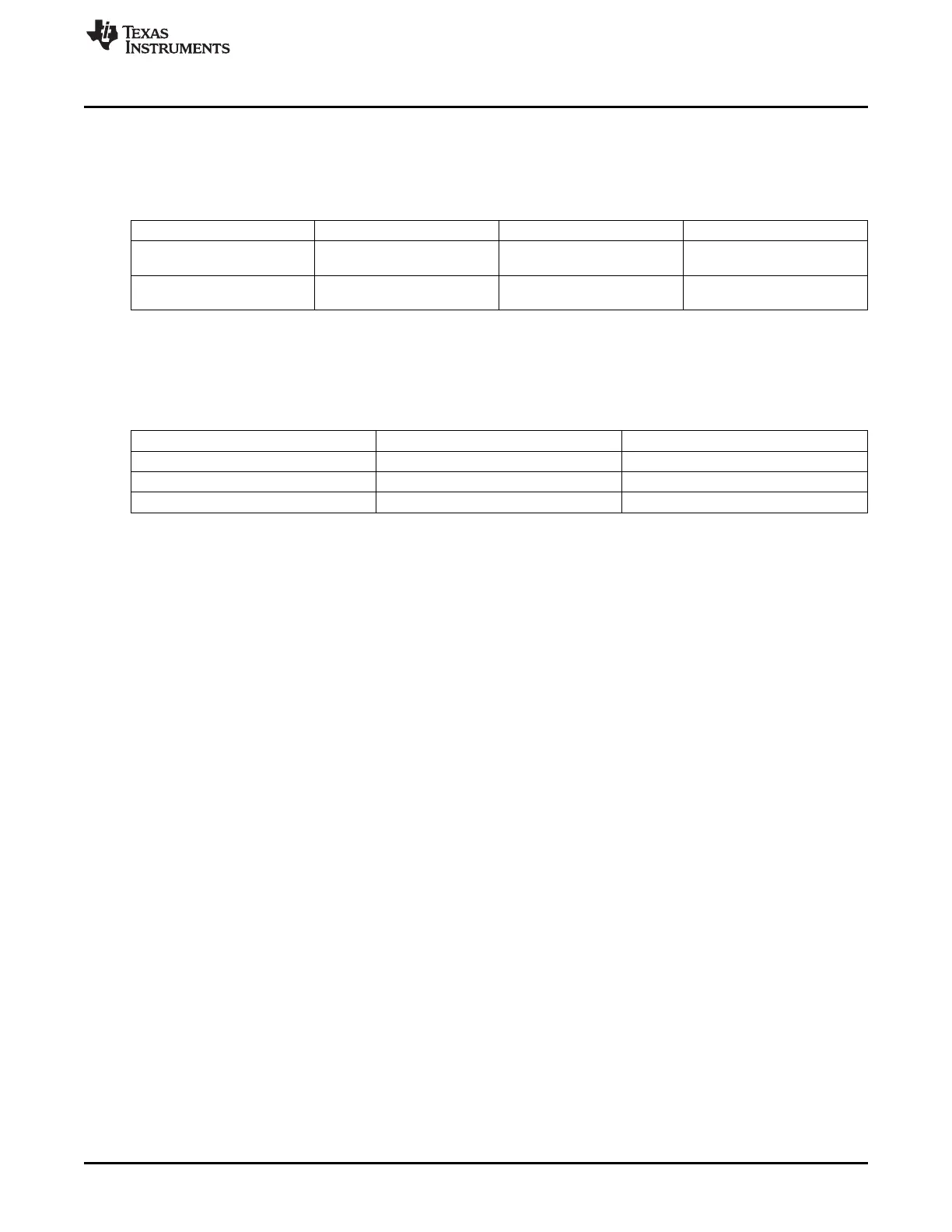

The TSC_ADC external interface signals are shown in Table 12-3.

Table 12-3. TSC_ADC Pin List

Pin Type Description

AN[7:0] I Analog Input

VREFN Power Analog Reference Input Negative Terminal

VREFP Power Analog Reference Input Positive Terminal

1025

SPRUH73H–October 2011–Revised April 2013 Touchscreen Controller

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...