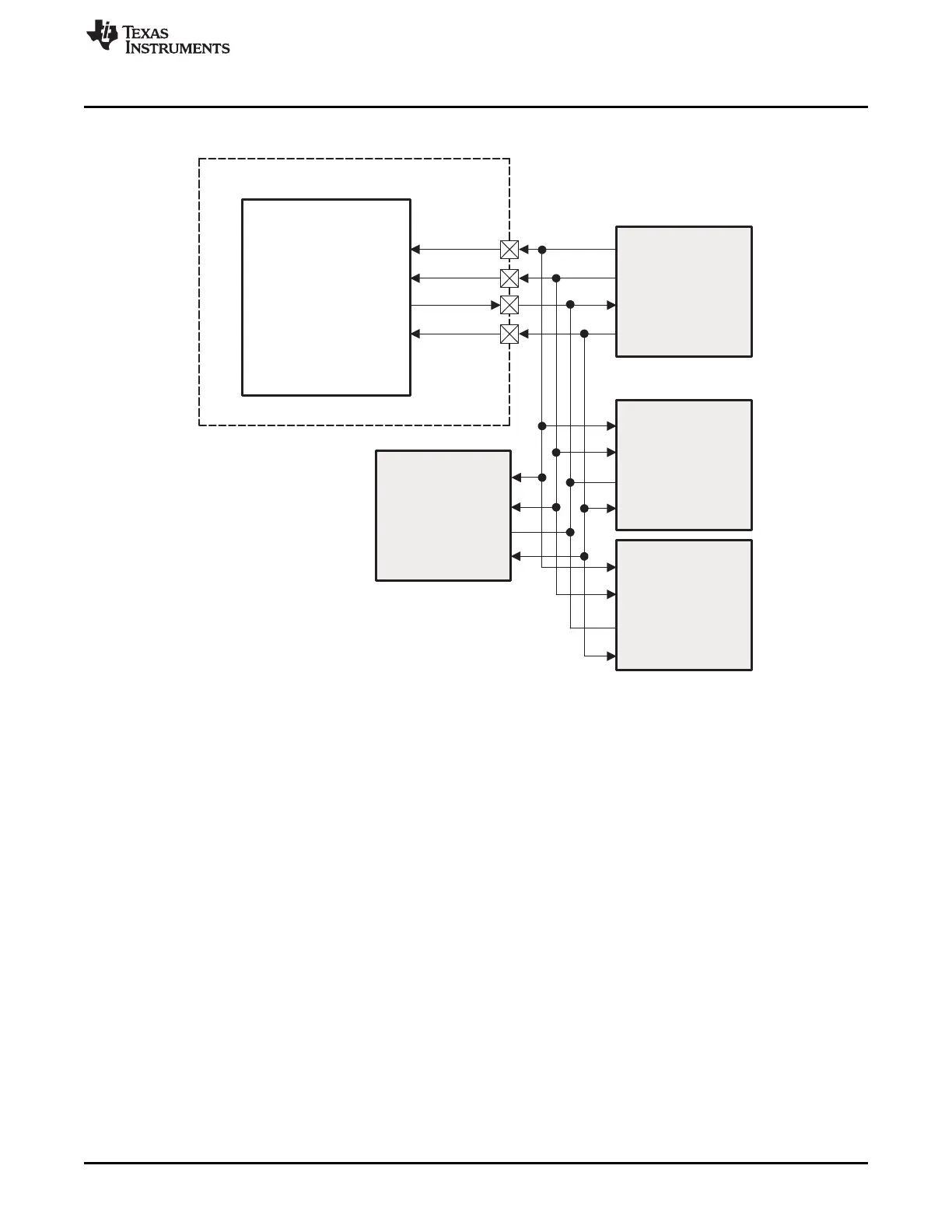

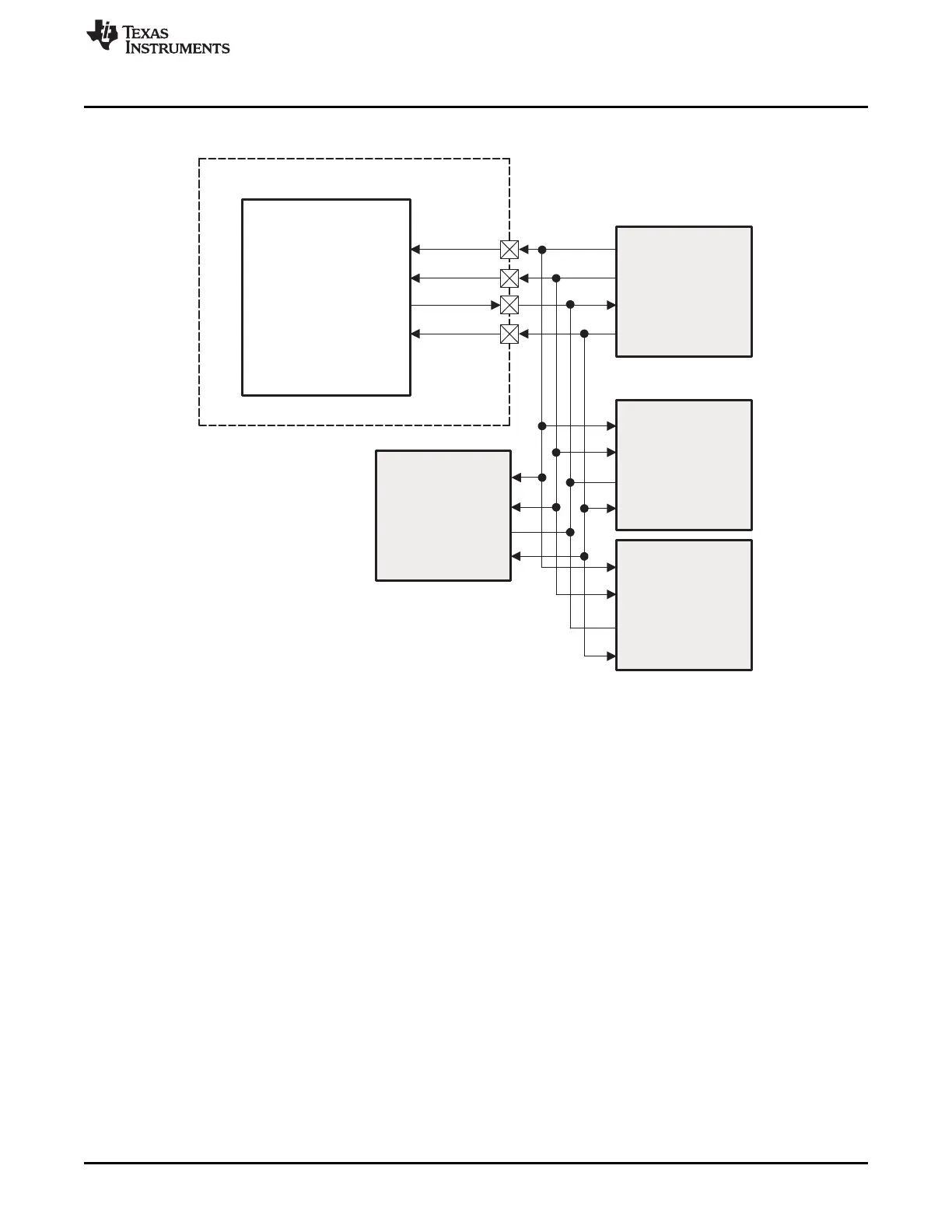

Device

spim_cs0

spim_somi

spim_simo

spim_clk

SIMO

SIMO

SIMO

SIMO

SCLK

SCLK

SCLK

SCLK

SOMI

SOMI

SOMI

SOMI

CS

CS

CS

CS

Generic

SPImaster

device

Generic

SPIslave

device

Generic

SPIslave

device

Generic

SPIslave

device

108-017

McSPI

modulem

www.ti.com

Functional Description

Figure 24-23. Example of SPI Slave with One Master and Multiple Slave Devices on Channel 0

24.3.3.2 Interrupt Events in Slave Mode

The interrupt events related to the transmitter register state are TX_empty and TX_underflow. The

interrupt events related to the receiver register state are RX_full and RX_overflow.

24.3.3.2.1 TX_EMPTY

The event TX_empty is activated when the channel is enabled and its transmitter register becomes empty.

Enabling channel automatically raises this event. When FIFO buffer is enabled

(MCSPI_CH(I)CONF[FFEW] set to 1), the TX_empty is asserted as soon as there is enough space in

buffer to write a number of byte defined by MCSPI_XFERLEVEL[AEL].

Transmitter register must be load to remove source of interrupt and TX_empty interrupt status bit must be

cleared for interrupt line de-assertion (if event enable as interrupt source).

When FIFO is enabled, no new TX_empty event will be asserted unless the host performs the number of

writes to the transmitter register defined by MCSPI_XFERLEVEL[AEL]. It is the responsibility of the Local

Host to perform the right number of writes.

4023

SPRUH73H–October 2011–Revised April 2013 Multichannel Serial Port Interface (McSPI)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...