www.ti.com

LCD Registers

13.5.23 IRQSTATUS Register (offset = 5Ch) [reset = 0h]

IRQSTATUS is shown in Figure 13-41 and described in Table 13-36.

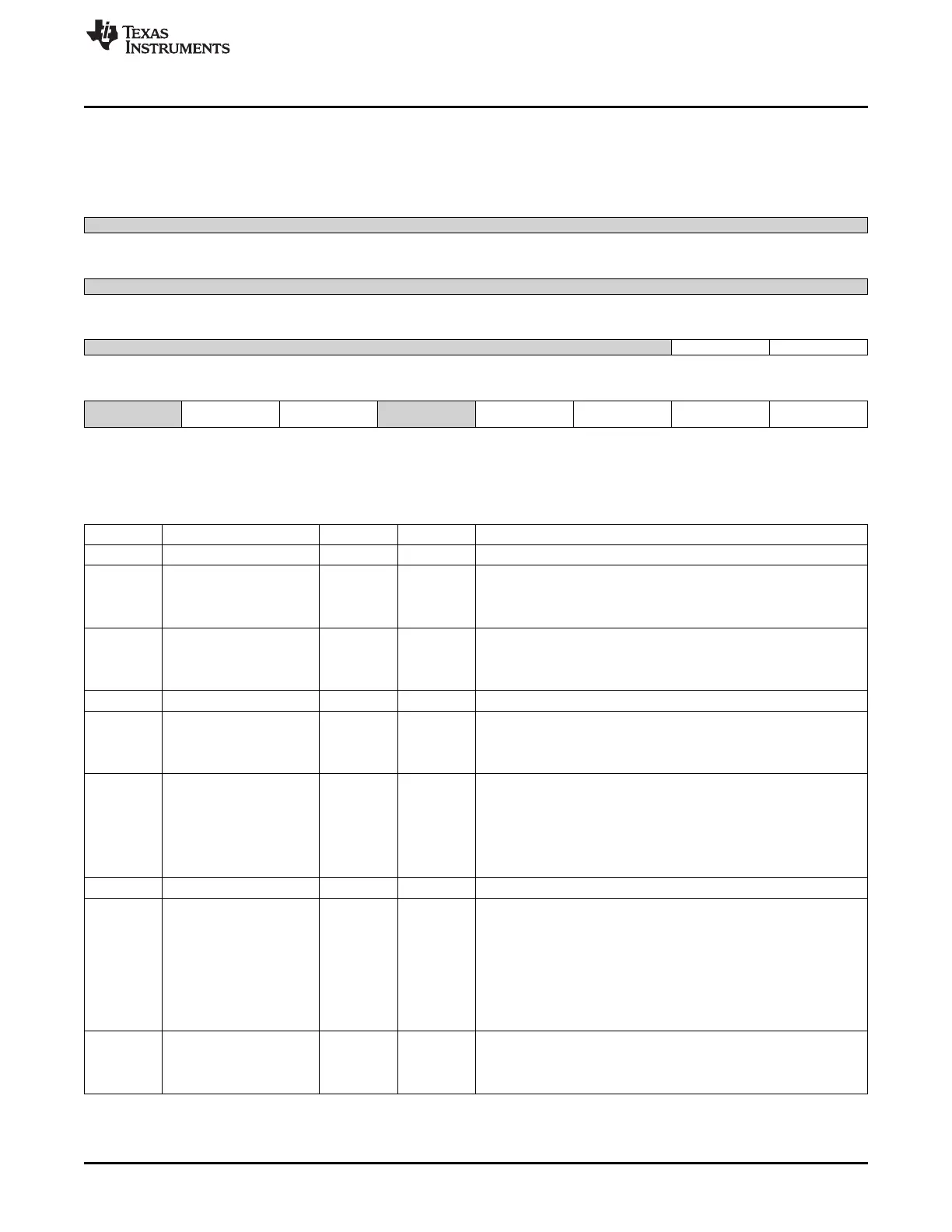

Figure 13-41. IRQSTATUS Register

31 30 29 28 27 26 25 24

Reserved

R/W-0h

23 22 21 20 19 18 17 16

Reserved

R/W-0h

15 14 13 12 11 10 9 8

Reserved eof1_en_clr eof0_en_clr

R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

Reserved pl_en_clr fuf_en_clr Reserved acb_en_clr sync_en_clr recurrent_raster_done done_en_clr

_en_clr

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

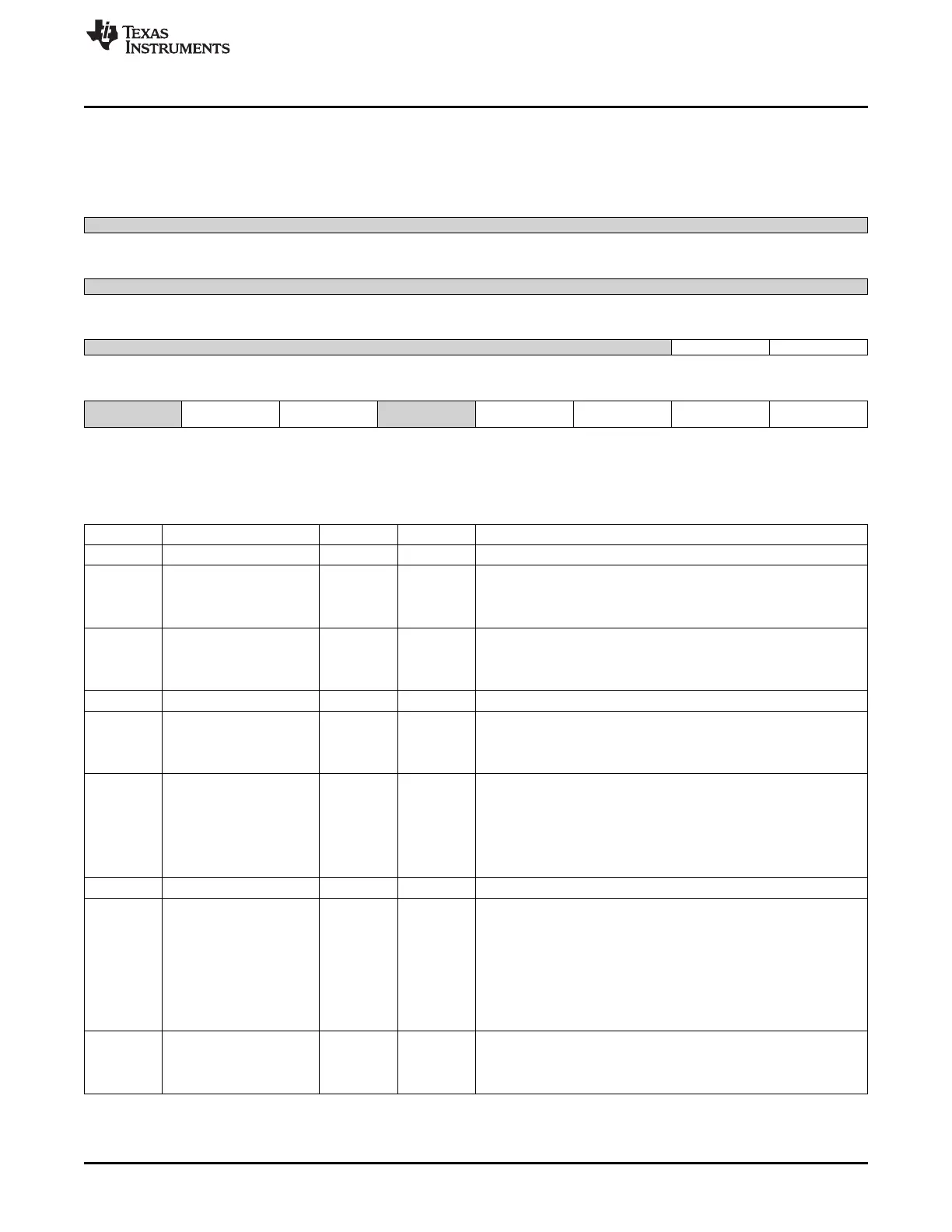

Table 13-36. IRQSTATUS Register Field Descriptions

Bit Field Type Reset Description

31-10 Reserved R/W 0h

9 eof1_en_clr R/W 0h DMA End-of-Frame 1 Enabled Interrupt and Clear Read indicates

enabled (masked) status 0 = inactive 1 = active Writing 1 will clear

interrupt enable

Writing 0 has no effect

8 eof0_en_clr R/W 0h DMA End-of-Frame 0 Enabled Interrupt and Clear Read indicates

enabled (masked) status 0 = inactive 1 = active Writing 1 will clear

interrupt enable

Writing 0 has no effect

7 Reserved R/W 0h

6 pl_en_clr R/W 0h DMA Palette Loaded Enabled Interrupt and Clear Read indicates

enabled (masked) status 0 = inactive 1 = active Writing 1 will clear

interrupt enable

Writing 0 has no effect

5 fuf_en_clr R/W 0h DMA FIFO Underflow Enabled Interrupt and Clear LCD dithering

logic not supplying data to FIFO at a sufficient rate, FIFO has

completely emptied and data pin driver logic has attempted to take

added data from FIFO

Read indicates enabled (masked) status 0 = inactive 1 = active

Writing 1 will clear interrupt enable

Writing 0 has no effect

4 Reserved R/W 0h

3 acb_en_clr R/W 0h For Passive Matrix Panels Only AC Bias Count Enabled Interrupt

and Clear AC bias transition counter has decremented to zero,

indicating that the lcd_ac_o line has transitioned the number of times

which is specified by the acbi control bit-field

The counter is reloaded with the value in acbi but it is disabled until

the user clears ABC

Read indicates enabled (masked) status 0 = inactive 1 = active

Writing 1 will clear interrupt enable

Writing 0 has no effect

2 sync_en_clr R/W 0h Frame Synchronization Lost Enabled Interrupt and Clear Read

indicates enabled status 0 = inactive 1 = active Writing 1 will clear

interrupt enable

Writing 0 has no effect

1155

SPRUH73H–October 2011–Revised April 2013 LCD Controller

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...