EDMA3 Registers

www.ti.com

11.4.2.5.4 Error Details Register (ERRDET)

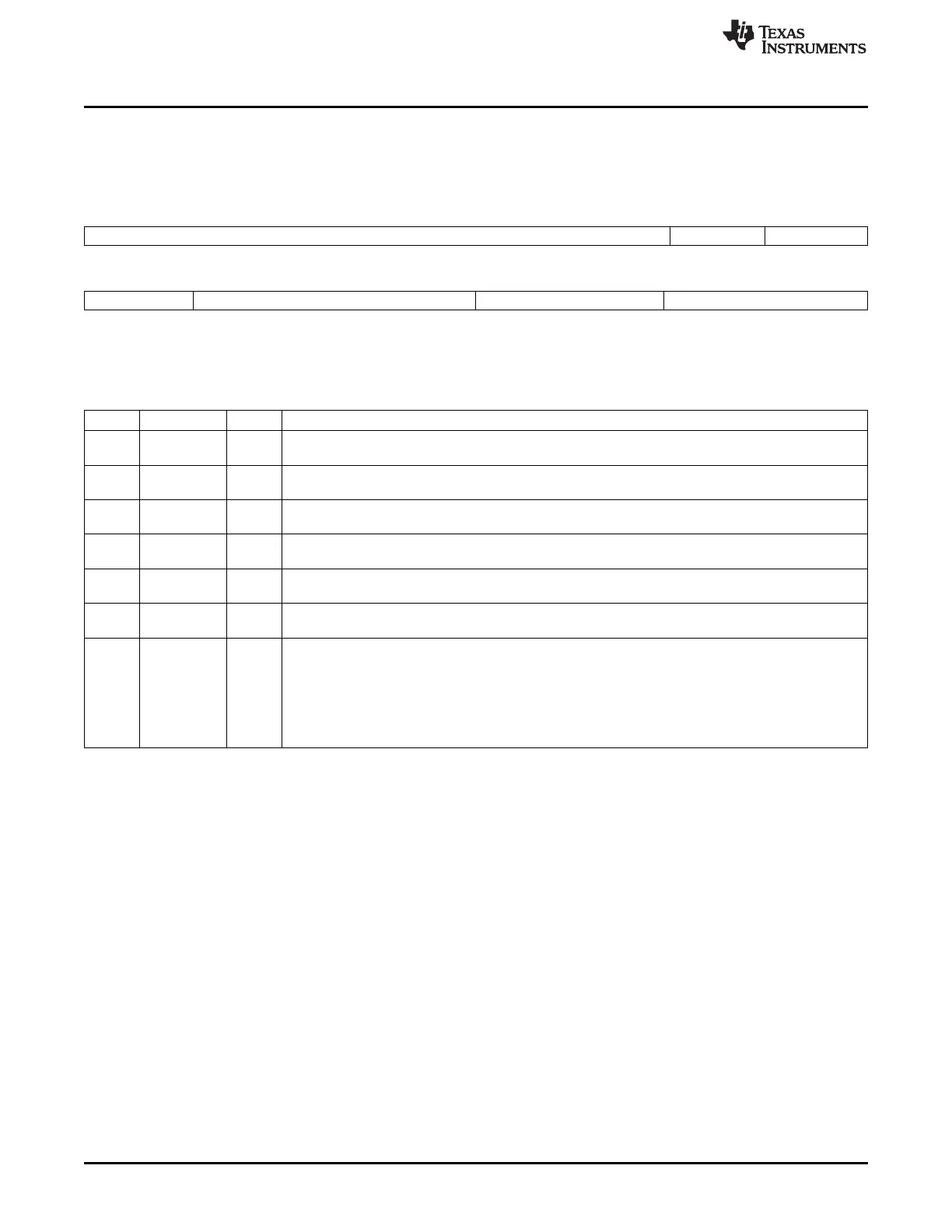

The error details register (ERRDET) is shown in Figure 11-112 and described in Table 11-97.

Figure 11-112. Error Details Register (ERRDET)

31 18 17 16

Reserved TCCHEN TCINTEN

R-0 R-0 R-0

15 14 13 8 7 4 3 0

Reserved TCC Reserved STAT

R-0 R-0 R-0 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

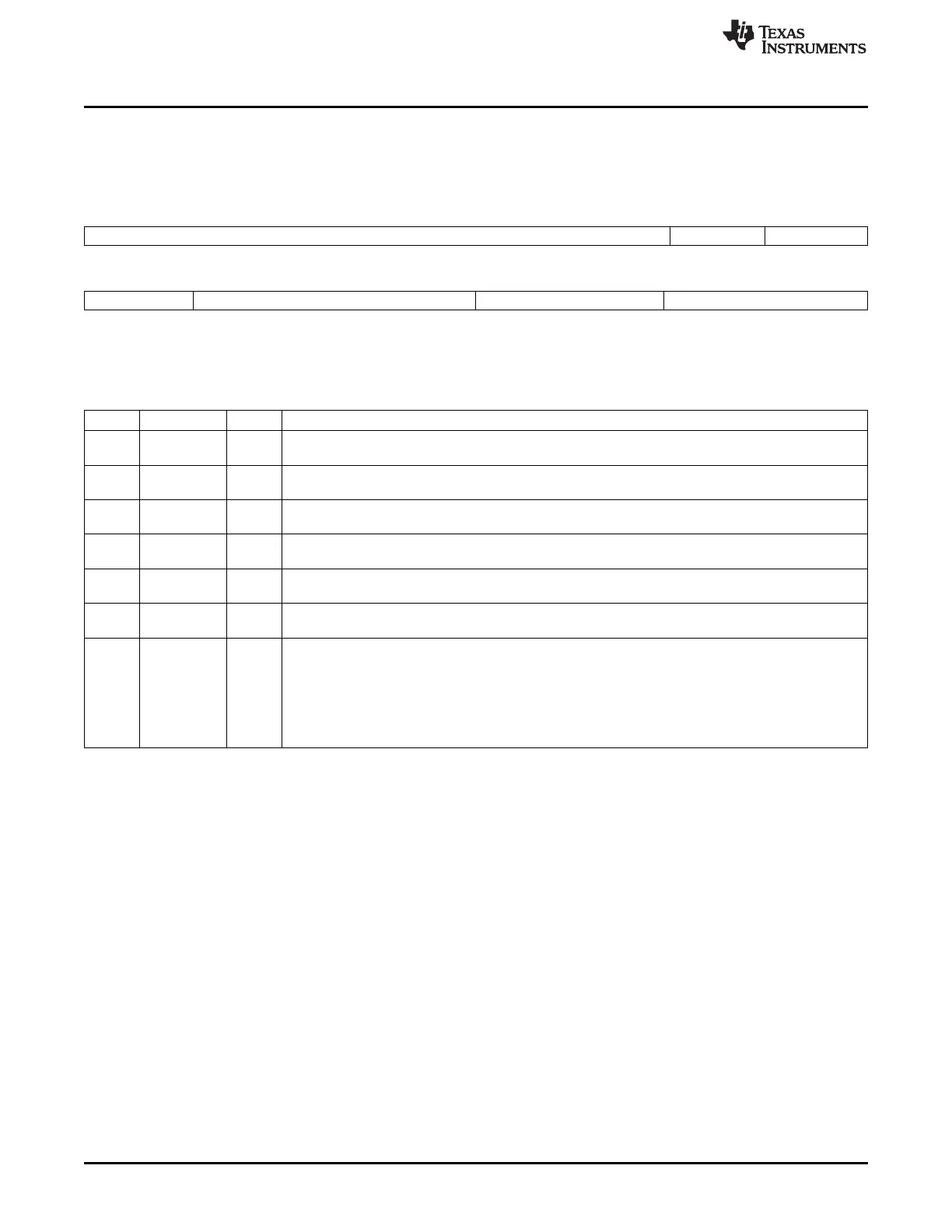

Table 11-97. Error Details Register (ERRDET) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

17 TCCHEN 0-1 Transfer completion chaining enable. Contains the TCCHEN value in the channel options parameter

(OPT) programmed by the channel controller for the read or write transaction that resulted in an error.

16 TCINTEN 0-1 Transfer completion interrupt enable. Contains the TCINTEN value in the channel options parameter

(OPT) programmed by the channel controller for the read or write transaction that resulted in an error.

15-14 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

13 - 8 TCC 0-3Fh Transfer complete code. Contains the TCC value in the channel options parameter (OPT) programmed

by the channel controller for the read or write transaction that resulted in an error.

7-4 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

3-0 STAT 0-Fh Transaction status. Stores the nonzero status/error code that was detected on the read status or write

status bus. If read status and write status are returned on the same cycle, then the EDMA3TC chooses

nonzero version. If both are nonzero, then the write status is treated as higher priority.

0 No error.

1h-7h Read error.

8h-Fh Write error.

1002

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...