Introduction

www.ti.com

– McASP1 32-bit target port

– ADC_TSC 32-bit target port

– USB 32-bit target port

– MMHCS2 32-bit target port

– L4_WKUP wakeup 32-bit target port

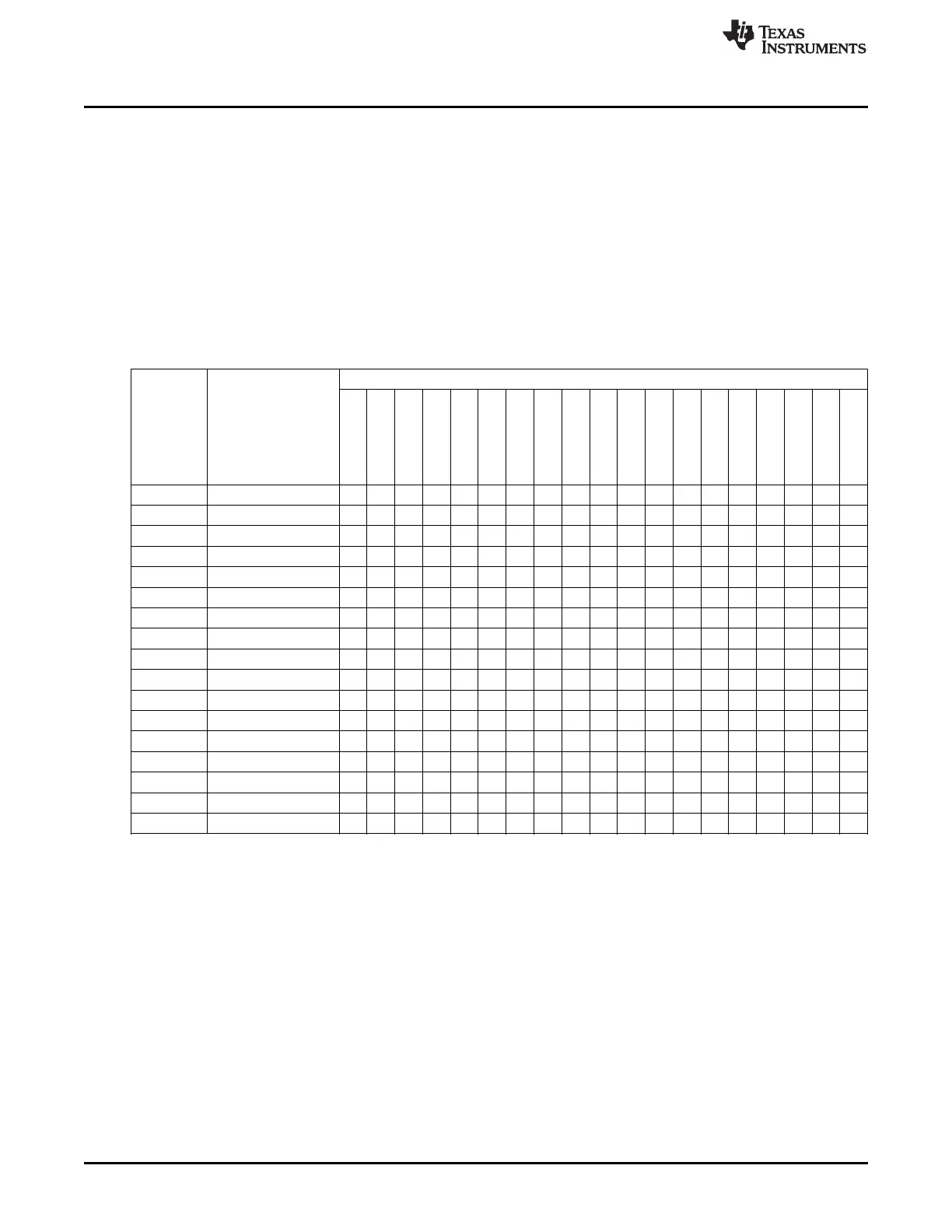

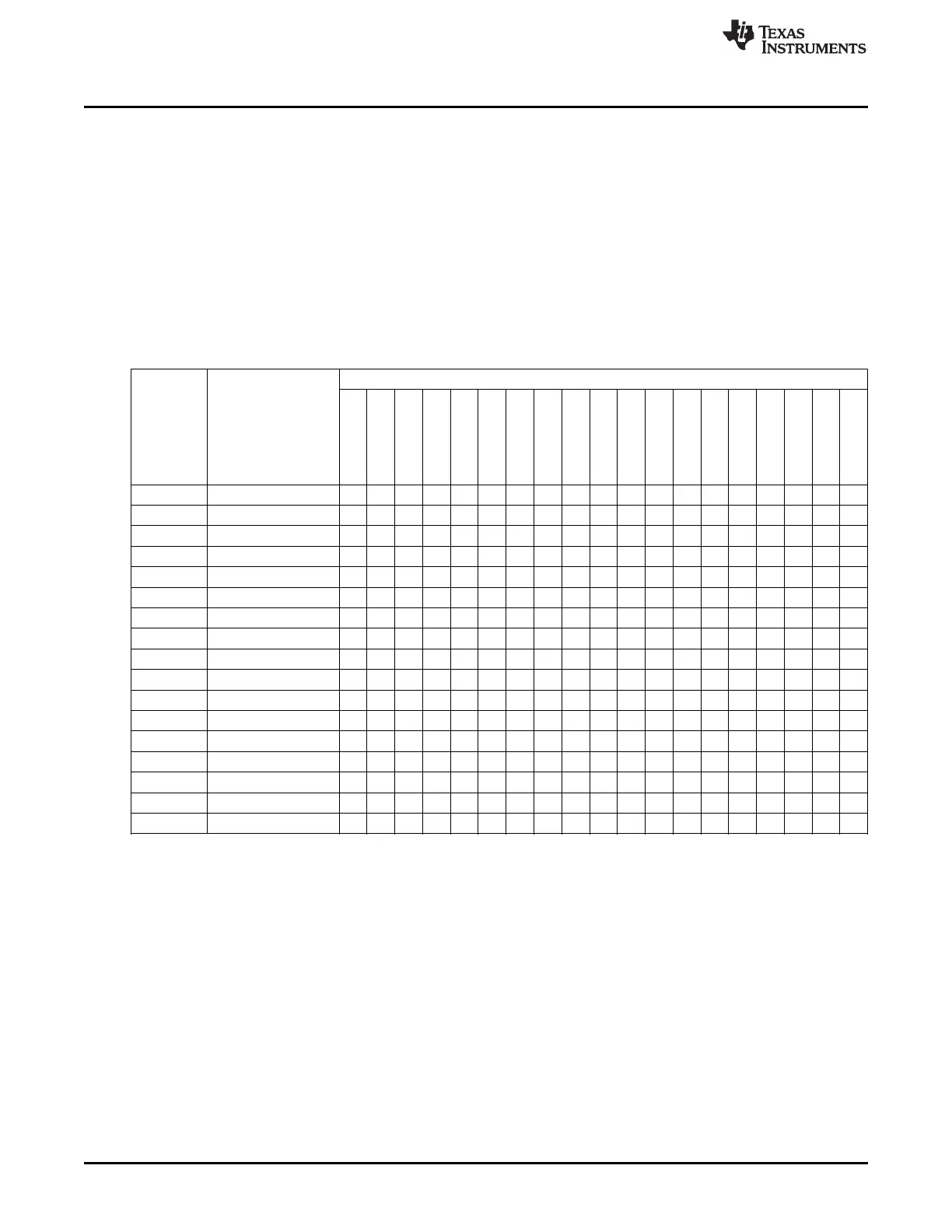

10.1.2.3 Interconnect Requirements

The required L3 connections between bus masters and slave ports are shown in Table 10-1. The L3

interconnect will return an address-hole error if any initiator attempts to access a target to which it has no

connection.

Table 10-1. L3 Master — Slave Connectivity

Slaves

EMIF

TPCC

Master ID Masters

GPMC

L4_FW

L4_Fast

SGX530

USBCFG

DebugSS

MMCHS2

L4_WKUP

ADC / TSC

OCMC-RAM

L4_PER ort0

TPTC0–2 FG

L4_PER Port1

Expansion Slot

L4_PER Port 2

L4_PER Port 3

NOC Registers

0x00 MPUSS M1 (128-bit) R

0x00 MPUSS M2 (64-bit) R R R R R R R R R R R R R R R R

0x18 TPTC0 RD R R R R R R R R R R R

0x19 TPTC0 WR R R R R R R R R R R R R

0x1A TPTC1 RD R R R R R R R R R R R

0x1B TPTC1 WR R R R R R R R R R R R

0x1C TPTC2 RD R R R R R R R R R R R

0x1D TPTC2 WR R R R R R R R R R R R

0x24 LCD Controller R R R

0x0E PRU-ICSS (PRU0) R R R R R R R R R R R R

0x0F PRU-ICSS (PRU1) R R R R R R R R R R R R

0x30 GEMAC R R R

0x20 SGX530 R R R

0x34 USB0 DMA R R

0x35 USB1 Queue Mgr R R R

0x04 EMU (DAP) R R R R R R R R R R R R R R R R

0x05 IEEE1500 R R R R R R R R R R R R R R R R

866

Interconnects SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...