www.ti.com

I2C Registers

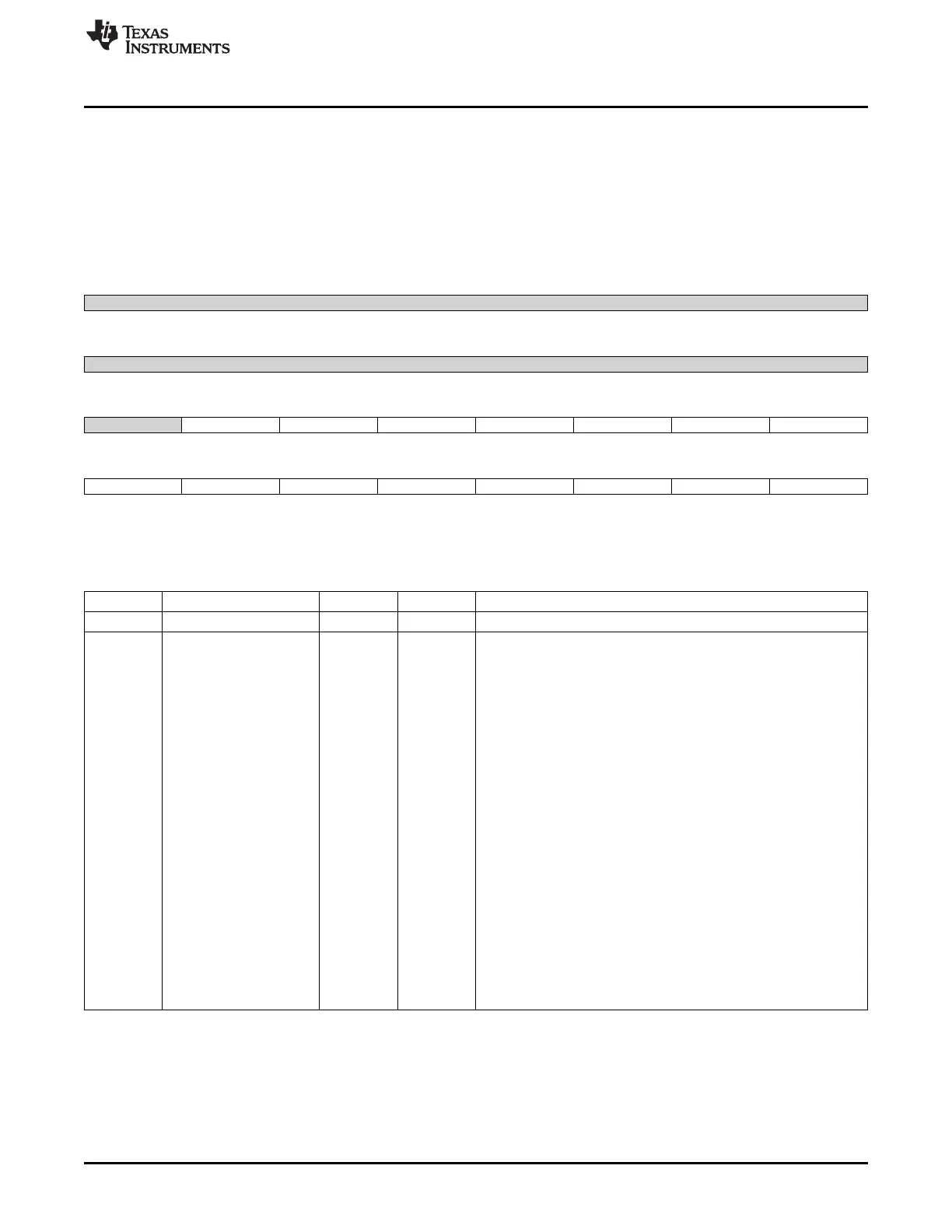

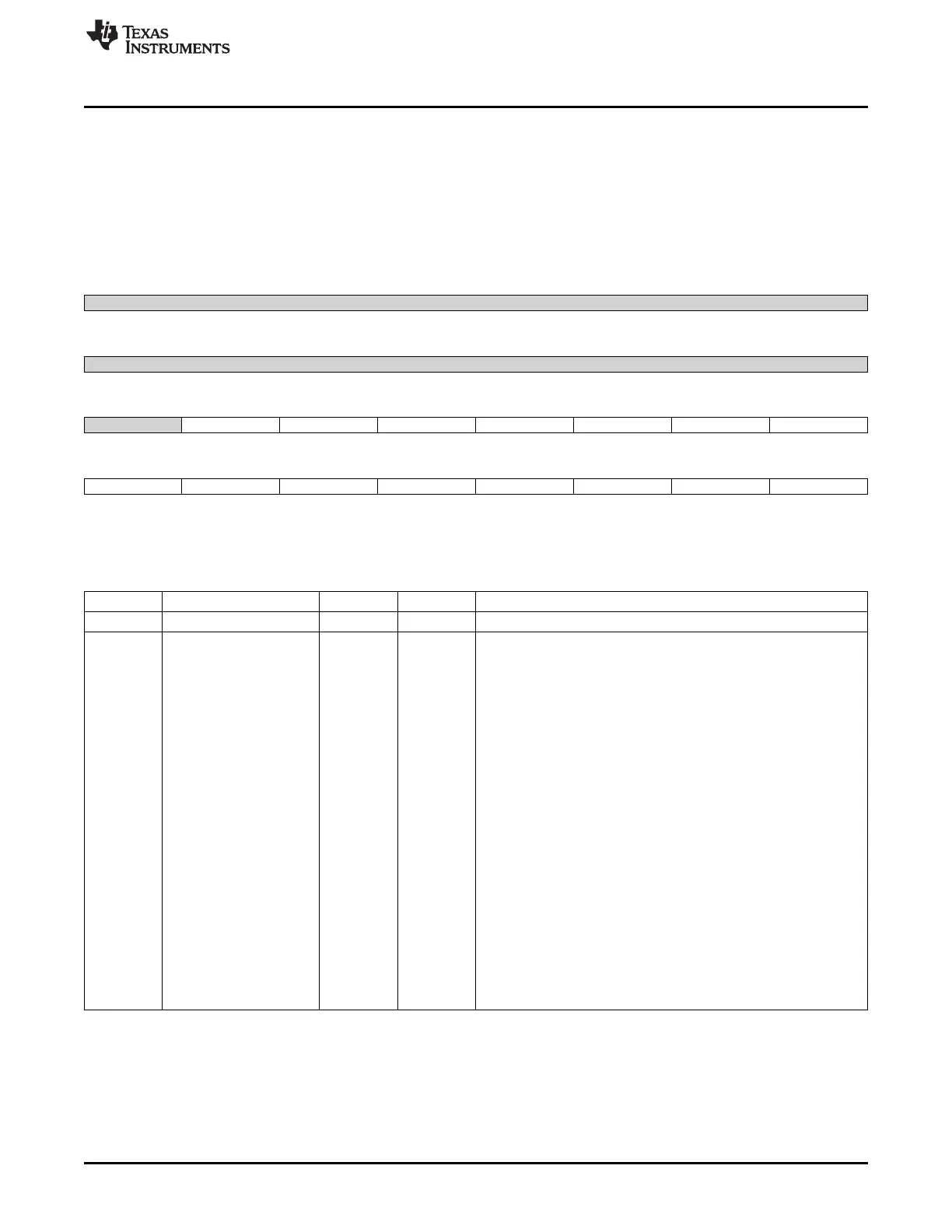

21.4.1.4 I2C_IRQSTATUS_RAW Register (offset = 24h) [reset = 0h]

I2C_IRQSTATUS_RAW is shown in Figure 21-19 and described in Table 21-12.

This register provides core status information for interrupt handling, showing all active events (enabled

and not enabled). The fields are read-write. Writing a 1 to a bit will set it to 1, that is, trigger the IRQ

(mostly for debug). Writing a 0 will have no effect, that is, the register value will not be modified. Only

enabled, active events will trigger an actual interrupt request on the IRQ output line.

Figure 21-19. I2C_IRQSTATUS_RAW Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved XDR RDR BB ROVR XUDF AAS BF

R-0h R/W-0h R/W-0h R-0h R/W-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

AERR STC GC XRDY RRDY ARDY NACK AL

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

Table 21-12. I2C_IRQSTATUS_RAW Register Field Descriptions

Bit Field Type Reset Description

31-15 Reserved R 0h

14 XDR R/W 0h Transmit draining IRQ status.

I2C Master Transmit mode only.

This read/clear only bit is set to 1 when the module is configured as

a master transmitter, the TX FIFO level is below the configured

threshold (TXTRSH) and the amount of data still to be transferred is

less than TXTRSH.

When this bit is set to 1 by the core, CPU must read the

I2C_BUFSTAT.TXSTAT register in order to check the amount of

data that need to be written in the TX FIFO.

Then, according to the mode set (DMA or interrupt), the CPU can

enable the DMA draining feature of the DMA controller with the

number of data bytes to be transferred (I2C_BUFSTAT.TXSTAT), or

generate write data accesses according to this value (IRQ mode).

The interrupt needs to be cleared after the DMA controller was

reconfigured (if DMA mode enabled), or before generating data

accesses to the FIFO (if IRQ mode enabled).

If the corresponding interrupt was enabled, an interrupt is signaled to

the local host.

The CPU can also poll this bit.

For more details about TDR generation, refer to the FIFO

Management subsection.

The CPU can only clear this bit by writing a 1 into this register.

A write 0 has no effect.

Value after reset is low.

0x0 = Transmit draining inactive

0x1 = Transmit draining enabled

3721

SPRUH73H–October 2011–Revised April 2013 I2C

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...