www.ti.com

GPMC

7.1.5.6 GPMC_TIMEOUT_CONTROL

The GPMC_TIMEOUT_CONTROL register allows the user to set the start value of the timeout counter

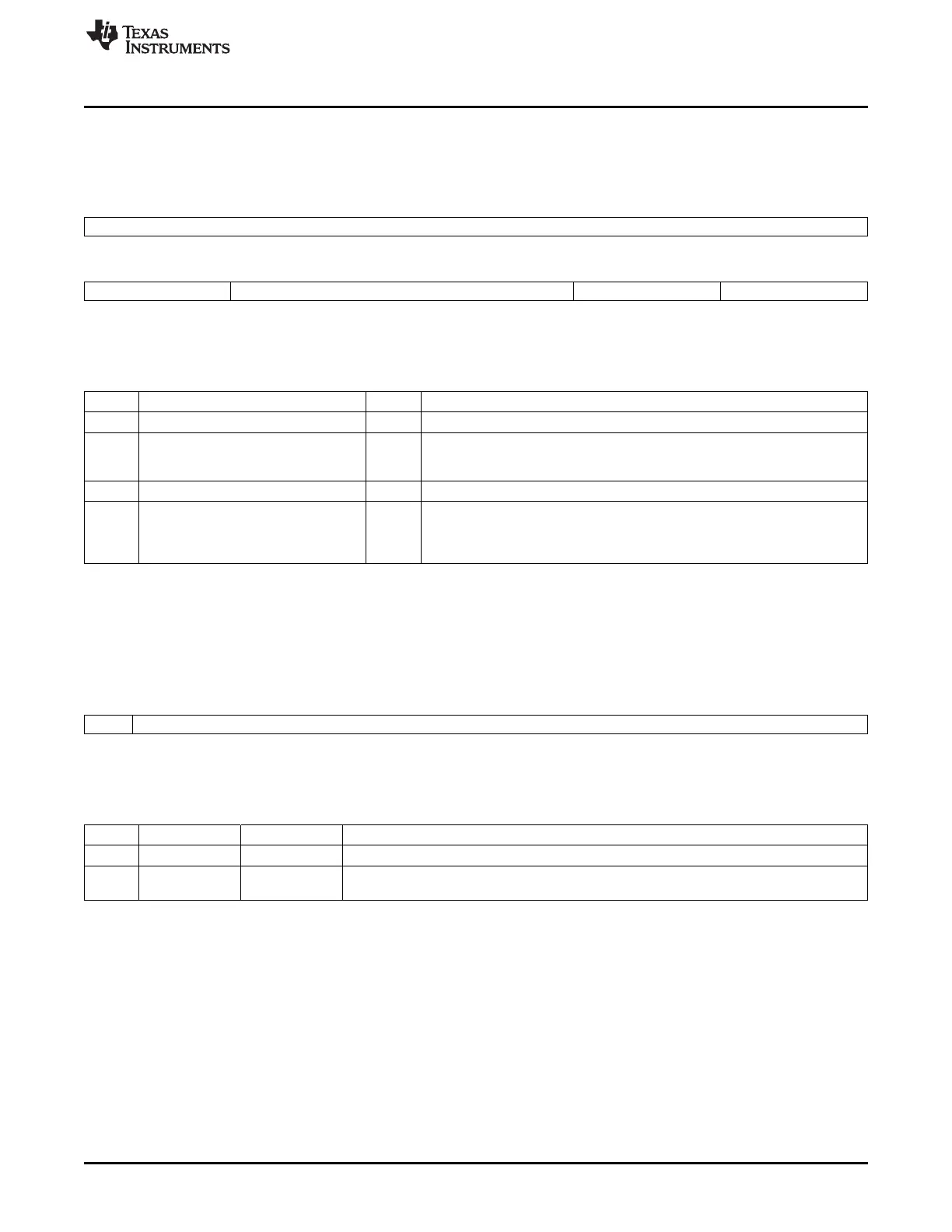

Figure 7-56. GPMC_TIMEOUT_CONTROL

31 16

Reserved

R-0

15 13 12 4 3 1 0

Reserved TIMEOUTSTARTVALUE Reserved TIMEOUTENABLE

R-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-60. GPMC_TIMEOUT_CONTROL Field Descriptions

Bit Field Value Description

31-13 Reserved 0 Reserved

12-4 TIMEOUTSTARTVALUE 0-1FFh Start value of the time-out counter (000 corresponds to 0 GPMC.FCLK cycle,

1h corresponds to 1 GPMC.FCLK cycle, and 1FFh corresponds to 511

GPMC.FCLK cycles)

3-1 Reserved 0 Reserved

0 TIMEOUTENABLE Enable bit of the TimeOut feature

0 TimeOut feature is disabled

1 TimeOut feature is enabled

7.1.5.7 GPMC_ERR_ADDRESS

The GPMC_ERR_ADDRESS register stores the address of the illegal access when an error occurs.

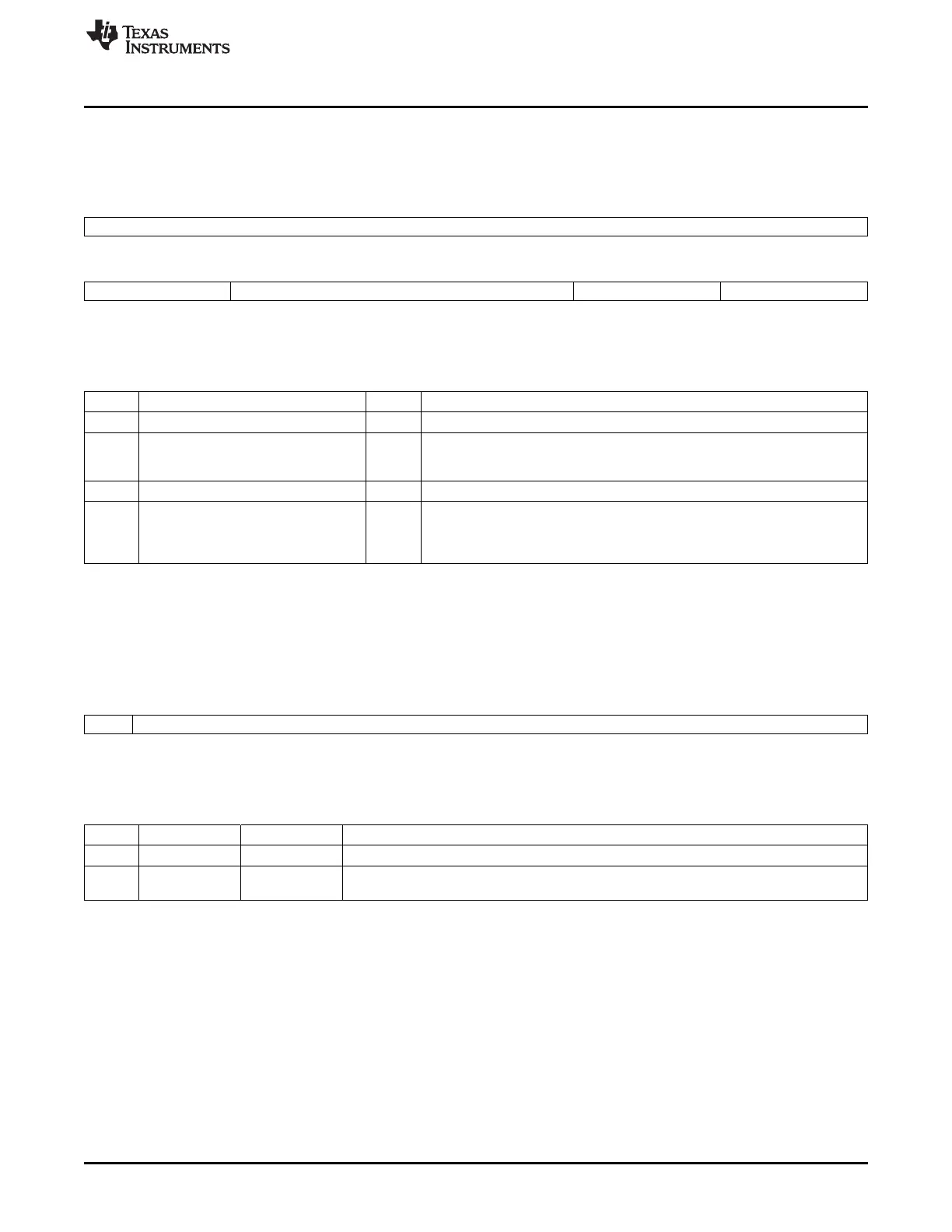

Figure 7-57. GPMC_ERR_ADDRESS

31 30 0

Rsvd ILLEGALADD

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-61. GPMC_ERR_ADDRESS Field Descriptions

Bit Field Value Description

31 Reserved 0 Reserved

30-0 ILLEGALADD 0-7FFF FFFFh Address of illegal access: A30 (0 for memory region, 1 for GPMC register region) and A29-

A0 (1GByte maximum)

371

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...