www.ti.com

Power, Reset, and Clock Management

8.1.13.1.4 PRM_IRQSTATUS_M3 Register (offset = Ch) [reset = 0h]

PRM_IRQSTATUS_M3 is shown in Figure 8-167 and described in Table 8-182.

This register provides status on MPU interrupt events. An event is logged whether interrupt generation for

the event is enabled or not. SW is required to clear a set bit by writing a '1' into the bit-position to be

cleared.

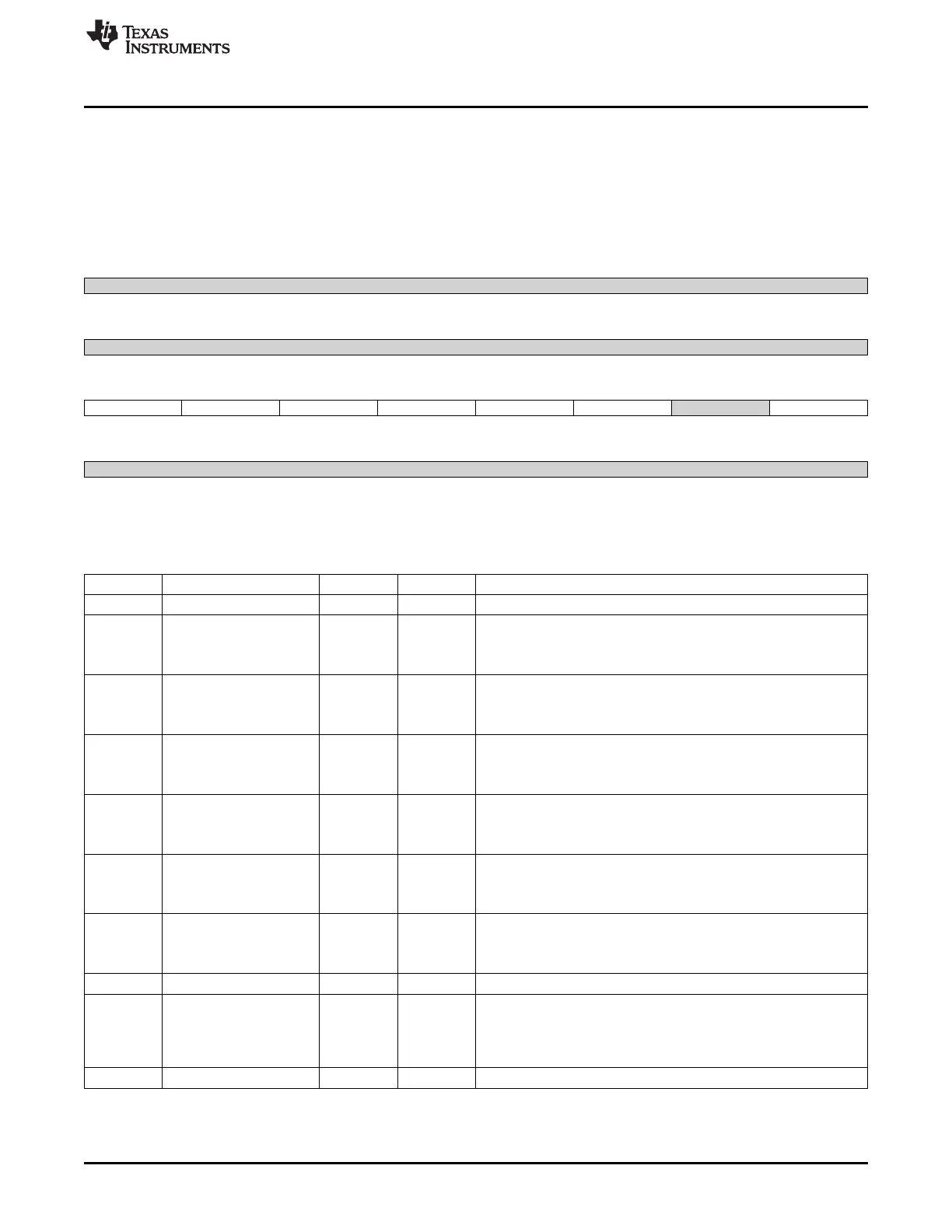

Figure 8-167. PRM_IRQSTATUS_M3 Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

dpll_per_recal_st dpll_ddr_recal_st dpll_disp_recal_st dpll_core_recal_st dpll_mpu_recal_st ForceWkup_st Reserved Transition_st

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R-0h R/W-0h

7 6 5 4 3 2 1 0

Reserved

R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

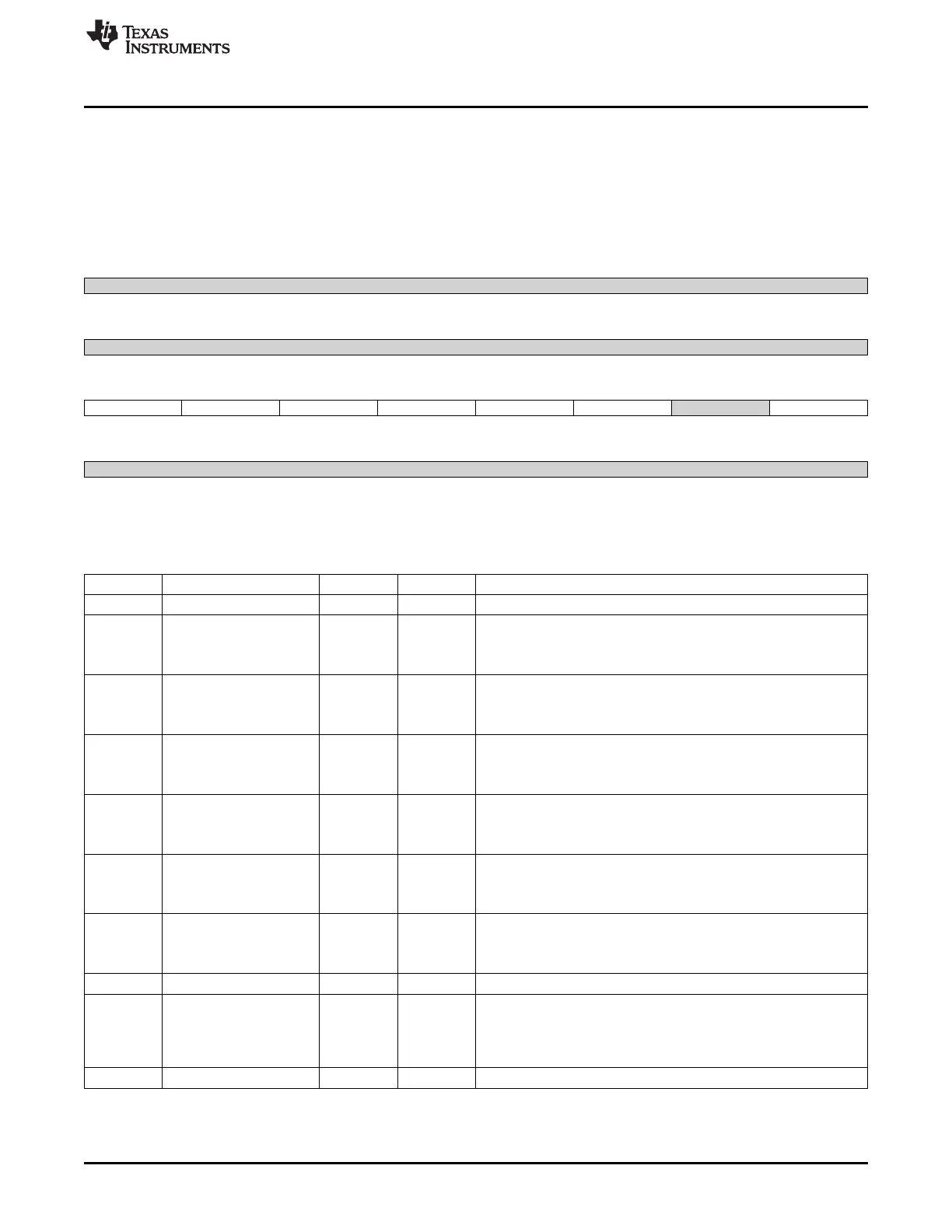

Table 8-182. PRM_IRQSTATUS_M3 Register Field Descriptions

Bit Field Type Reset Description

31-16 Reserved R 0h

15 dpll_per_recal_st R/W 0h

interrupt status for usb dpll recaliberation

0 = DIS : Disables dpll recaliberation

1 = EN : ENAbles dpll recaliberation

14 dpll_ddr_recal_st R/W 0h

interrupt status for ddr dpll recaliberation

0 = DIS : Disables dpll recaliberation

1 = EN : ENAbles dpll recaliberation

13 dpll_disp_recal_st R/W 0h

interrupt status for disp dpll recaliberation

0 = DIS : Disables dpll recaliberation

1 = EN : ENAbles dpll recaliberation

12 dpll_core_recal_st R/W 0h

interrupt status for core dpll recaliberation

0 = DIS : Disables dpll recaliberation

1 = EN : ENAbles dpll recaliberation

11 dpll_mpu_recal_st R/W 0h

interrupt status for mpu dpll recaliberation

0 = DIS : Disables dpll recaliberation

1 = EN : ENAbles dpll recaliberation

10 ForceWkup_st R/W 0h

Software supervised wakeup completed event interrupt status

0 = IRQ_fal : No interrupt

1 = IRQ_tru : Interrupt is pending

9 Reserved R 0h

8 Transition_st R/W 0h

Software supervised transition completed event interrupt status (any

domain)

0 = IRQ_fal : No interrupt

1 = IRQ_tru : Interrupt is pending

7-0 Reserved R 0h

709

SPRUH73H–October 2011–Revised April 2013 Power, Reset, and Clock Management (PRCM)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...