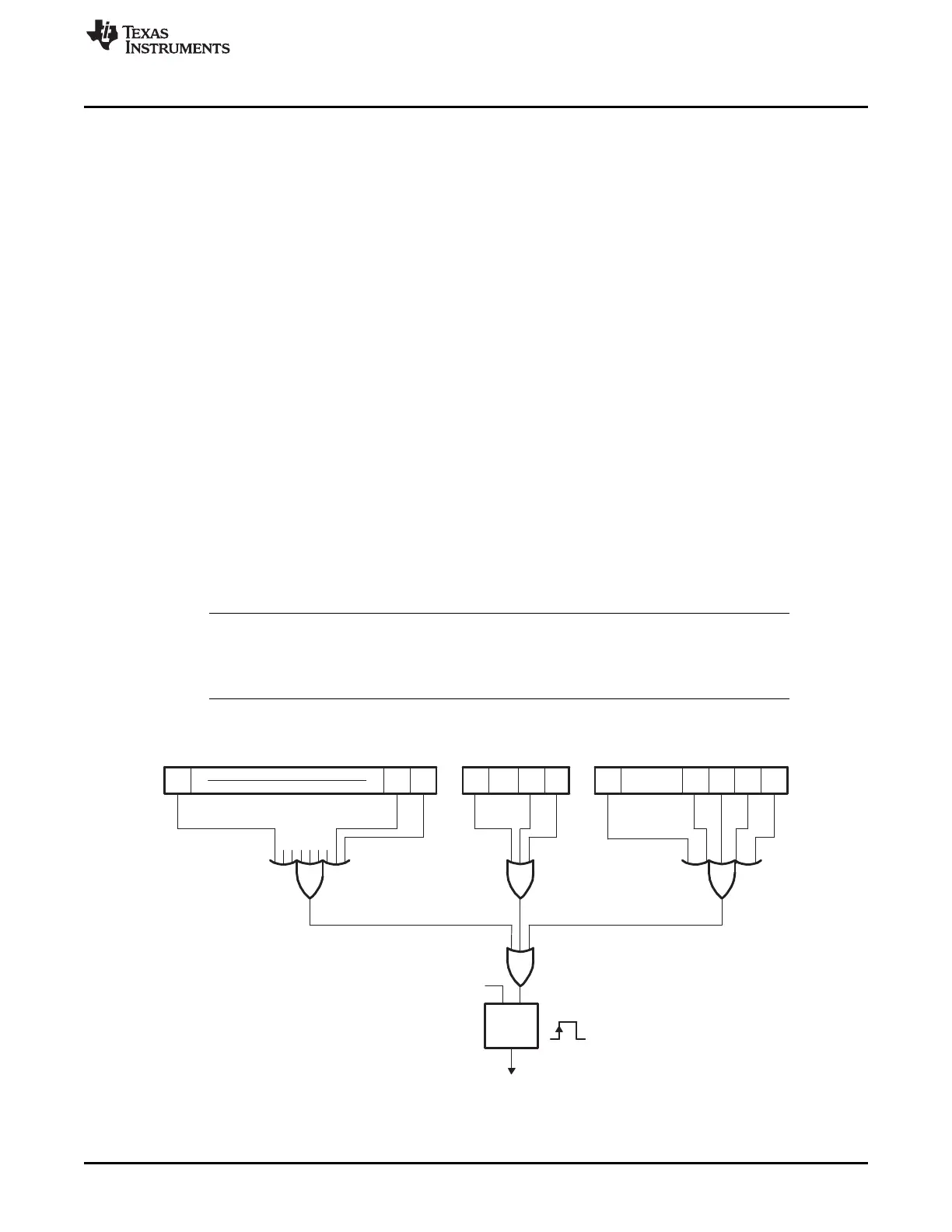

16 1 0

CCERR

7

QEMR

1 0

EMR/EMRH

63 1 0

EDMACC_ERRINT

EEVAL.EVAL

pulse

Eval/

3 2... .......

www.ti.com

Functional Description

11.3.9.4 Error Interrupts

The EDMA3CC error registers provide the capability to differentiate error conditions (event missed,

threshold exceed, etc.). Additionally, setting the error bits in these registers results in asserting the

EDMA3CC error interrupt. If the EDMA3CC error interrupt is enabled in the device interrupt controller(s),

then it allows the CPU(s) to handle the error conditions.

The EDMA3CC has a single error interrupt (EDMA3CC_ERRINT) that is asserted for all EDMA3CC error

conditions. There are four conditions that cause the error interrupt to pulse:

• DMA missed events: for all 64 DMA channels. DMA missed events are latched in the event missed

registers (EMR/EMRH).

• QDMA missed events: for all 8 QDMA channels. QDMA missed events are latched in the QDMA event

missed register (QEMR).

• Threshold exceed: for all event queues. These are latched in EDMA3CC error register (CCERR).

• TCC error: for outstanding transfer requests that are expected to return completion code (TCCHEN or

TCINTEN bit in OPT is set to 1) exceeding the maximum limit of 63. This is also latched in the

EDMA3CC error register (CCERR).

Figure 11-17 illustrates the EDMA3CC error interrupt generation operation.

If any of the bits are set in the error registers due to any error condition, the EDMA3CC_ERRINT is always

asserted, as there are no enables for masking these error events. Similar to transfer completion interrupts

(EDMA3CC_INT), the error interrupt also only pulses when the error interrupt condition transitions from no

errors being set to at least one error being set. If additional error events are latched prior to the original

error bits clearing, the EDMA3CC does not generate additional interrupt pulses.

To reduce the burden on the software, there is an error evaluate register (EEVAL) that allows re-

evaluation of pending set error events/bits, similar to the interrupt evaluate register (IEVAL). You can use

this so that the CPU(s) does not miss any error events.

NOTE: It is good practice to enable the error interrupt in the device interrupt controller and to

associate an interrupt service routine with it to address the various error conditions

appropriately. Doing so puts less burden on the software (polling for error status);

additionally, it provides a good debug mechanism for unexpected error conditions.

Figure 11-17. Error Interrupt Operation

907

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...