www.ti.com

Functional Description

13.3.6 Interrupt Conditions

13.3.6.1 Highlander 0.8 Interrupts

13.3.6.1.1 Highlander Interrupt Basics

The interrupt mechanism is Highlander 0.8-compliant and relies on the ipgvmodirq IP Generic. The

ipgvmodirq module supports hardware-initiated interrupts, each of which can also be individually triggered

by software. An interrupt mask function allows each interrupt to be masked or enabled. The software can

read all of the raw interrupts or only those that are unmasked.

All pending interrupts in the LCD module must be serviced by the Host’s Interrupt Service Routine before

it exits.

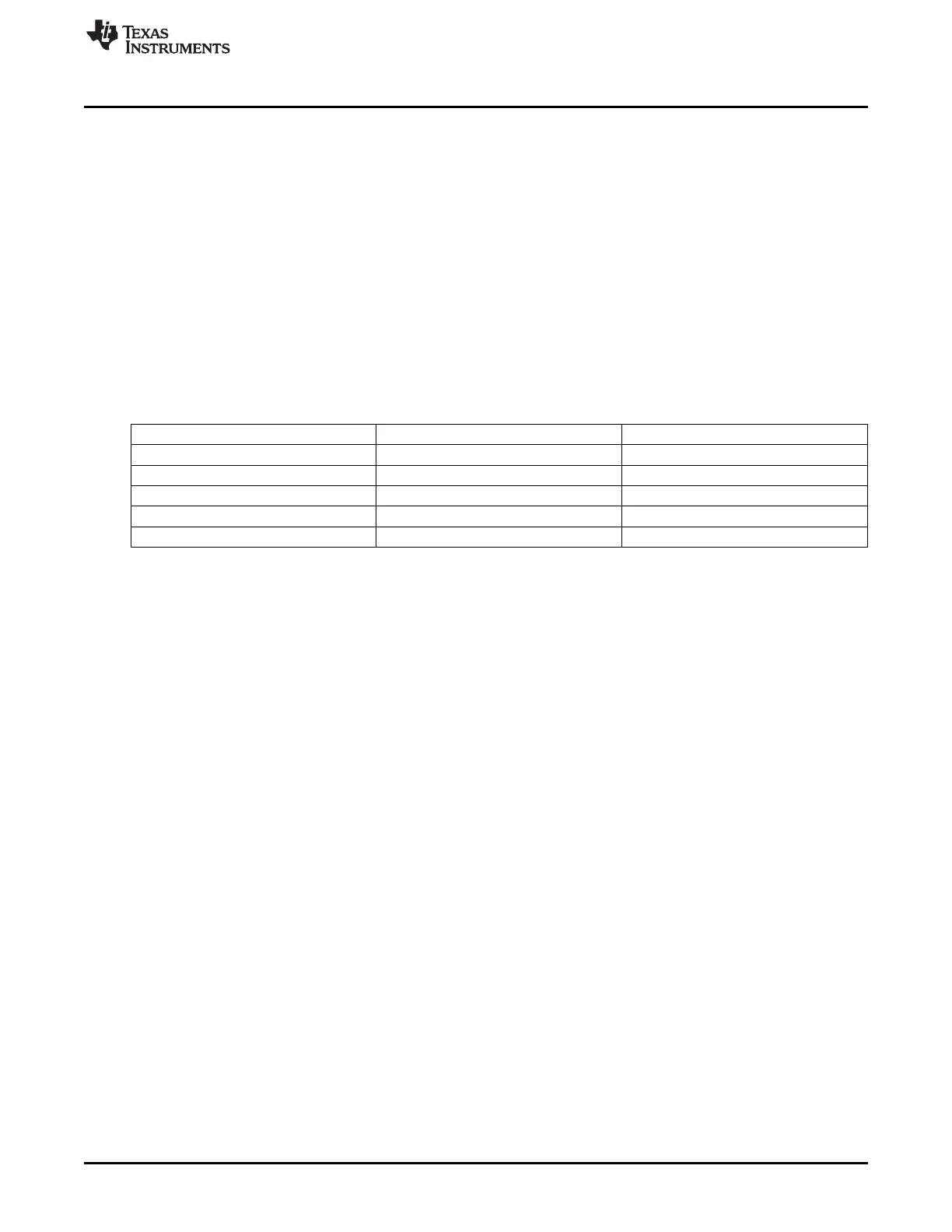

The Interrupt Module registers are described in the following table.

Table 13-12. Highlander 0.8 Interrupt Module Control Registers

Address Offset Name Description

0x58 Reg22 Interrupt Raw Status Register

0x5C Reg23 Interrupt Masked Status Register

0x60 Reg24 Interrupt Enable Set (Unmask)

0x64 Reg25 Interrupt Enable Clear (Mask)

0x68 Reg26 End of Interrupt Indicator

13.3.6.1.2 Raw Status Register

Interrupts are associated with a bit position. For instance, Hardware Interrupt 0 is physically connected to

bit 0 of the interrupt controller and all Sets, Clears, and Masks to this interrupt will reference the Bit 0

location of the interrupt vector. Likewise, Hardware Interrupt 1 is referenced by bit 1 of the interrupt vector,

and so on.

The Host CPU can see all the interrupts that have been set, regardless of the interrupt mask, by reading

Reg22, the Raw Status Register.

If the Host CPU writes a ‘1’ to a bit position in Reg 22, it will do a software set for the interrupt associated

with that bit position.

13.3.6.1.3 Masked Status Register

The Masked Status Register contains all the pending interrupts that are unmasked (enabled). The

Interrupt Service Routine should read this register to determine which interrupts must be serviced.

13.3.6.1.4 Interrupt Enable Set Register

To unmask an interrupt, the Host CPU writes a ‘1’ to the appropriate bit position of the Enable Set

(Unmask) register.

13.3.6.1.5 Interrupt Enable Clear Register

To mask an interrupt, the Host CPU writes a ‘1’ to the appropriate bit position of the Enable Clear (Mask)

register.

13.3.6.1.6 End of Interrupt Register

The ipgvmodirq module supports level or pulse interrupts to the CPU. For pulse interrupts, the Host must

write to an end-of-interrupt (EOI), memory-mapped address to indicate that the Interrupt Service Routine

has completed and is exiting. Any pending interrupts that have not been serviced will trigger another

interrupt pulse to the Host CPU.

1119

SPRUH73H–October 2011–Revised April 2013 LCD Controller

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...