www.ti.com

DMTimer

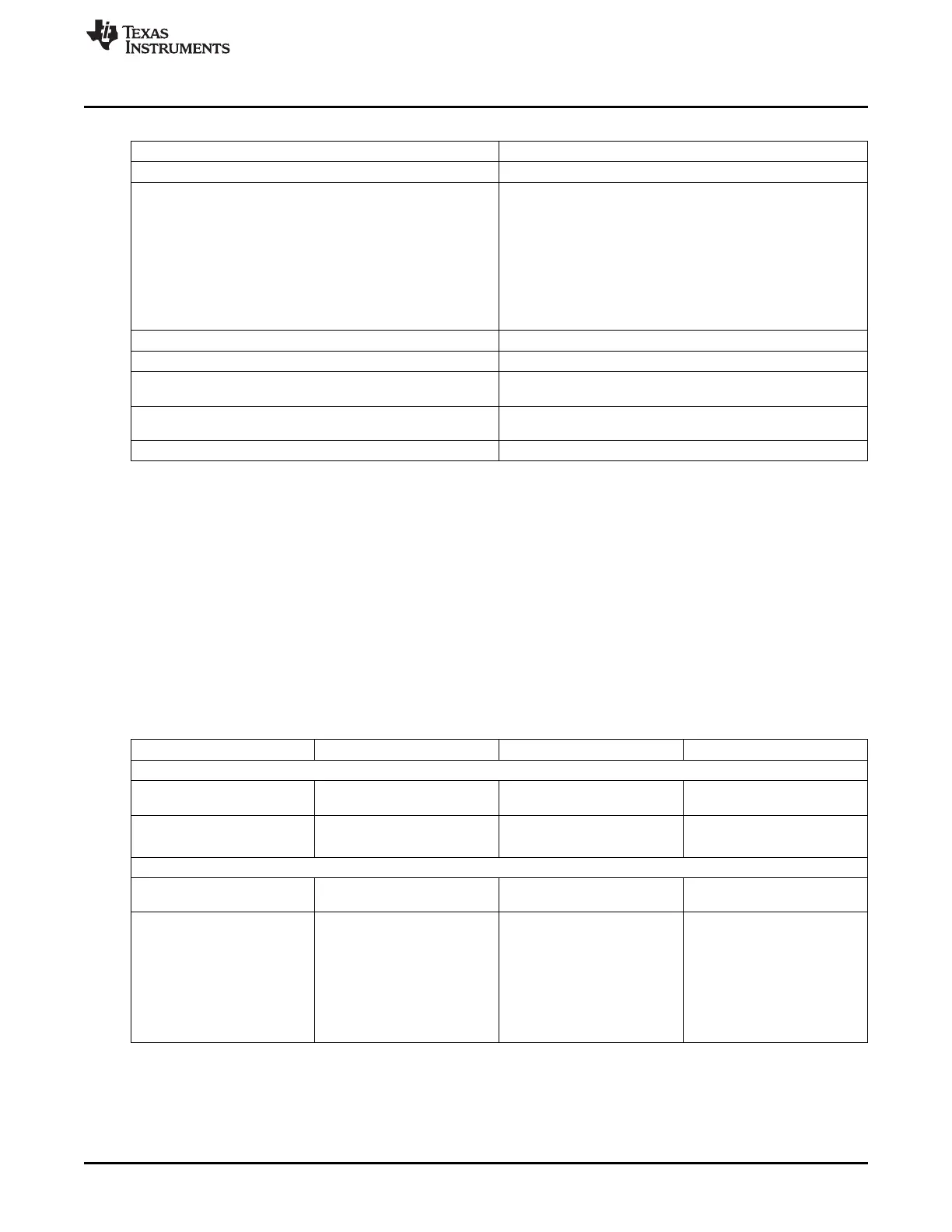

Table 20-3. Timer[2–7] Connectivity Attributes

Attributes Type

Power Domain Peripheral Domain

Clock Domain

PD_PER_L4LS_GCLK (OCP)

Functional Clocks:

PD_PER_TIMER2_GCLK (Timer 2)

PD_PER_TIMER3_GCLK (Timer 3)

PD_PER_TIMER4_GCLK (Timer 4)

PD_PER_TIMER5_GCLK (Timer 5)

PD_PER_TIMER6_GCLK (Timer 6)

PD_PER_TIMER7_GCLK (Timer 7)

Reset Signals PER_DOM_RST_N

Idle/Wakeup Signals Smart Idle (No wakeup capabilities)

Interrupt Requests 1 per timer module to MPU Subsystem (TINT2 - TINT7)

Also to TSC_ADC event capture mux for Timer 4–Timer7

DMA Requests Interrupt requests are redirected as DMA requests: 1 per

instance (TINTx)

Physical Address L4 Peripheral slave port

20.1.2.2 Timer Clock and Reset Management

Each DMTimer[2–7] functional clock is selected within the PRCM using the associated

CLKSEL_TIMERx_CLK register from 3 possible sources:

• The 24-MHz (typ) system clock (CLK_M_OSC)

• The PER PLL generated 32.768 KHz clock (CLK_32KHZ)

• The TCLKIN external timer input clock.

The DMTimer 0 functional clock is fixed to use the internal 32KHz RC Clock (CLK_RC32K).

20.1.2.3 Timer Clock Signals

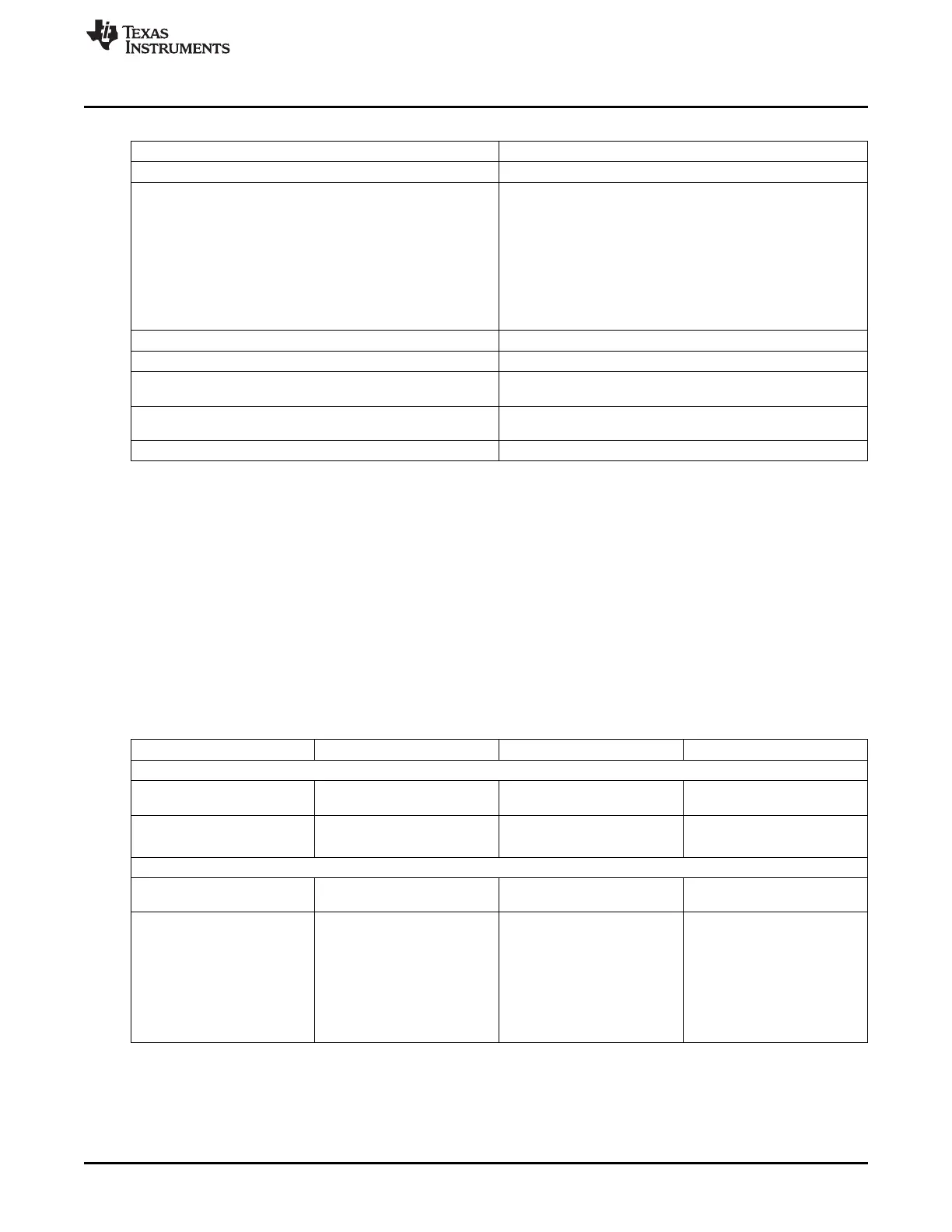

Table 20-4. Timer Clock Signals

Clock Signal Max Freq Reference / Source Comments

Timer[0] Clock Signals

PICLKOCP 100 MHz CORE_CLKOUTM4 / 2 pd_wkup_l4_wkup_gclk

Interface clock from PRCM

PICLKTIMER 25 MHz

(1)

pd_wkup_timer0_gclk

CLK_RC32K

Functional clock from PRCM

CLK_M_OSC

Timer[2–7] Clock Signals

PICLKOCP 100 MHz CORE_CLKOUTM4 / 2 pd_per_l4ls_gclk

Interface clock from PRCM

PICLKTIMER 25 MHz

(1)

CLK_M_OSC

pd_per_timer2_gclk

Functional clock CLK_32KHZ

pd_per_timer3_gclk

(PER_CLKOUTM2 / 5859.375)

pd_per_timer4_gclk

TCLKIN

pd_per_timer5_gclk

pd_per_timer6_gclk

pd_per_timer7_gclk

from PRCM

(1)

PICLKTIMER must be less than PICLKOCP/4.

3555

SPRUH73H–October 2011–Revised April 2013 Timers

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...