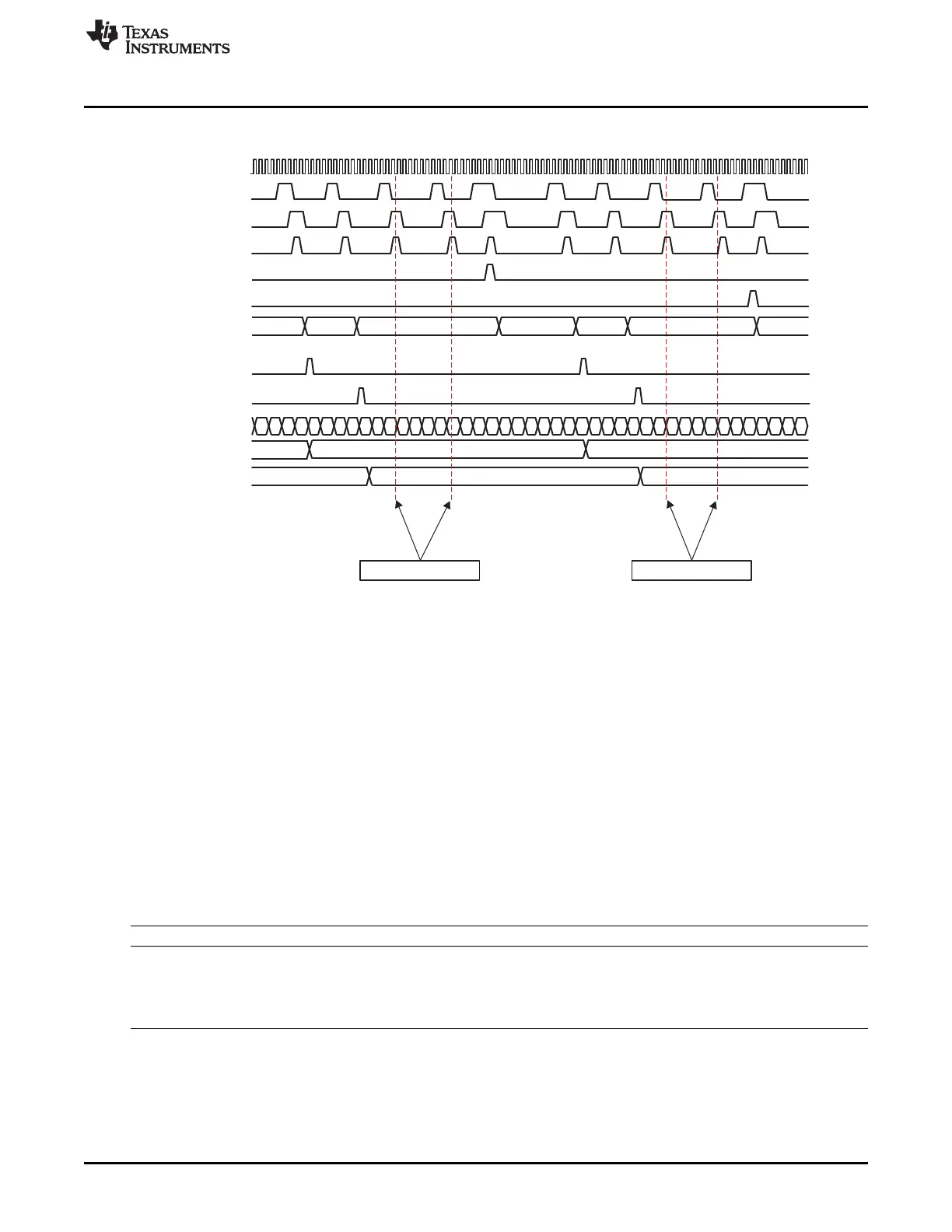

timer_clock

pi_eventcapt

eventcapt_resync

capt_pulse

int_serve

clear_trig

FSM State

tcar1_enable

TCRR

TCAR1

TCAR2

OCKED

LOCKED1

NEW_VALUE

Capture ignored

Capture ignored

NEW_VALUE

UN-LOCKEDLOCKED2

LOCKED1

UN-LOLOCKED2

tcar2_enable

NEW_VALUE NEW_VALUE

www.ti.com

DMTimer

Figure 20-6. Capture Wave Example for CAPT_MODE = 1

20.1.3.1.3 Compare Mode Functionality

When Compare Enable TCLR (CE bit) is set to 1, the timer value (TCRR) is permanently compared to the

value held in timer match register (TMAR). TMAR value can be loaded at any time (timer counting or

stop). When the TCRR and the TMAR values match, an interrupt can be issued if the IRQENABLE_SET

(MAT_EN_FLAG bit) is set. The right programming way is to write a compare value in TMAR register

before setting TCLR (CE bit) to avoid any unwanted interrupt due to a reset value matching effect.

The dedicated output pin (PORTIMERPWM) can be programmed through TCLR (TRG and PT bits) to

generate one positive pulse (TIMER clock duration) or to invert the current value (toggle mode) when an

overflow and a match occur.

20.1.3.1.4 Prescaler Functionality

A prescaler counter can be used to divide the timer counter input clock frequency. The prescaler is

enabled when TCLR bit 5 is set (PRE). The 2n division ratio value (PTV) can be configured in the TCLR

register. The prescaler counter is reset when the timer counter is stopped or reloaded on the fly.

Table 20-6. Prescaler Functionality

Contexts Prescaler Counter Timer Counter

Overflow (when Auto-reload on) Reset TLDR

TCRR Write Reset TCRR

TTGR Write Reset TLDR

Stop Reset Frozen

3559

SPRUH73H–October 2011–Revised April 2013 Timers

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...