EMIF

www.ti.com

Bits Value Description

DDR_A[1] reg_sdram_drive SDRAM drive strength from SDRAM Config register

DDR_A[0] 0x1 Disable DLL

• Starts an auto-refresh cycle in the next cycle.

• Enters its idle state and can issue any other commands except a write or a read. A write or a read will

only be issued after T_XSRD + 1 clock cycles have elapsed since DDR_CKE is driven high. The value

of T_XSRD is taken from SDRAM Timing 2 register.

Exit sequence of self-refresh mode for DDR3 device: The memory controller:

• Enables clocks.

• Drives DDR_CKE high.

• Waits for T_XSNR + 1 cycles. The value of T_XSNR is taken from SDRAM Timing 2 register.

• If the REG_DDR_DISABLE_DLL bit in the SDRAM Config register is 1, issues a LOAD MODE

REGISTER command to the extended mode register 1 with the pad_a_o bits set as follows:

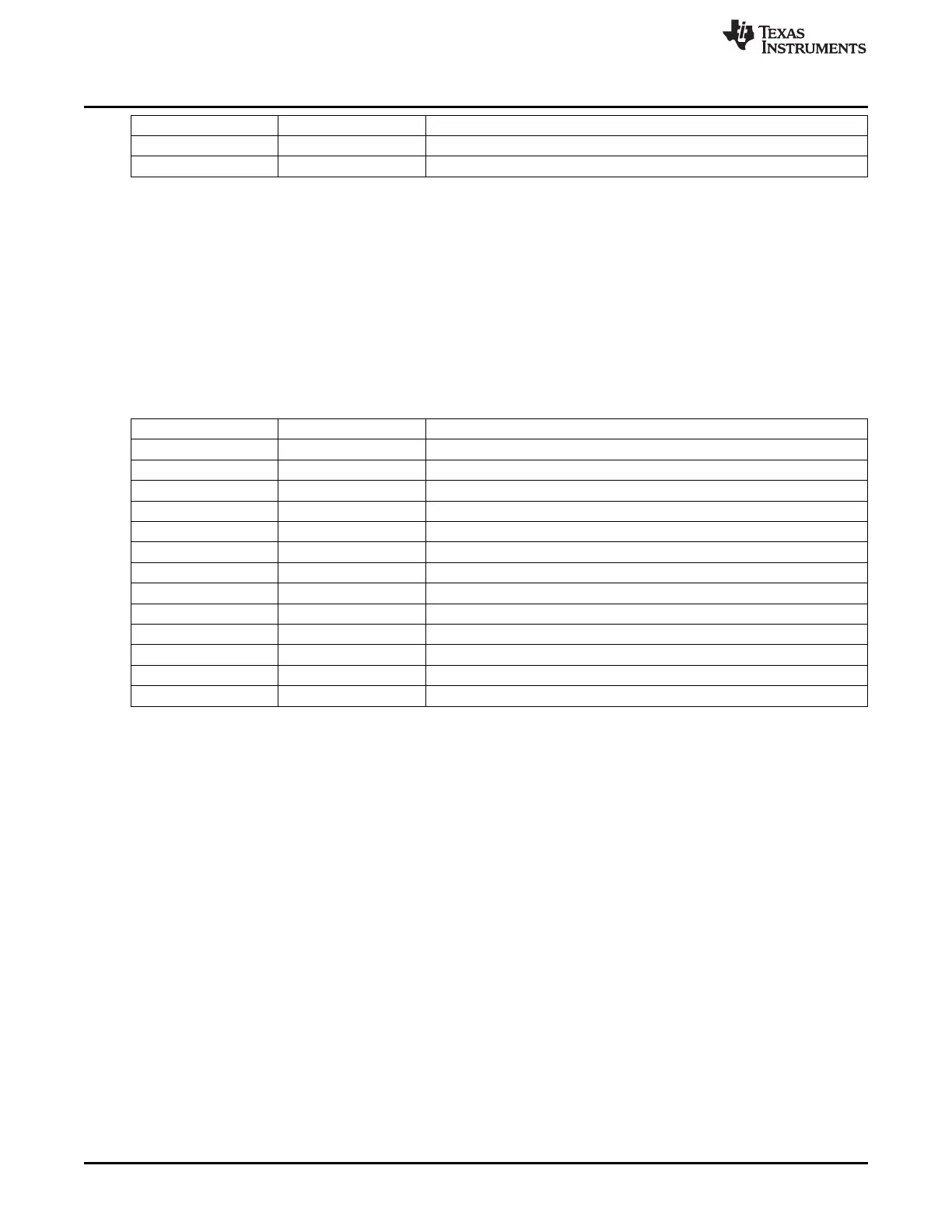

Bits Value Description

DDR_A[15:13] 0x0 Reserved

DDR_A[12] 0x0 Output buffer enabled

DDR_A[11] 0x0 TDQS disable

DDR_A[10] 0x0 Reserved

DDR_A[9] reg_ddr_term[2] DDR3 termination resistor value from SDRAM Config register

DDR_A[8] 0x0 Reserved

DDR_A[7] 0x0 Write leveling disabled

DDR_A[6] reg_ddr_term[1] DDR3 termination resistor value from SDRAM Config register

DDR_A[5] reg_sdram_drive[1] SDRAM drive strength from SDRAM Config register

DDR_A[4:3] 0x0 Additive latency = 0

DDR_A[2] reg_ddr_term[0] DDR3 termination resistor value from SDRAM Config register

DDR_A[1] reg_sdram_drive[0] SDRAM drive strength from SDRAM Config register

DDR_A[0] 0x1 Disable DLL

• Starts an auto-refresh cycle in the next cycle.

• Performs one write incremental leveling.

• Performs read DQS incremental training.

• Performs read data-eye incremental training.

• Enters its idle state and can issue any other commands except a write or a read. A write or a read will

only be issued after T_XSRD + 1 clock cycles have elapsed since DDR_CKE is driven high. The value

of T_XSRD is taken from SDRAM Timing 2 register.

7.3.3.11.3 Power Down Mode

The memory controller also supports power-down mode for low power. The memory controller

automatically puts the SDRAM into power-sDown after the memory controller is idle for REG_PD_TIM

number of DDR clock cycles and the REG_LP_MODE field is set to 4. The REG_LP_MODE and

REG_PD_TIM fields can be programmed in the Power Management Control register (PMCR). If the

Refresh Must level is not reached before the entry into power-down, the memory controller will not

precharge all banks before issuing the POWER-DOWN command. This will result in SDRAM entering

active power-down mode.

If the Refresh Must level is reached before the entry into power-down, the memory controller will

precharge all banks and issue refreshes until the Refresh Release Level is reached before issuing the

POWER-DOWN command. This will result in SDRAM entering precharge power-down mode.

In power-down mode, the memory controller does not stop the clocks DDR_CLK to the SDRAM. The

memory controller maintains DDR_CKE low to maintain the power-down state.

420

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...