www.ti.com

ARM Cortex-A8 Interrupts

6.3 ARM Cortex-A8 Interrupts

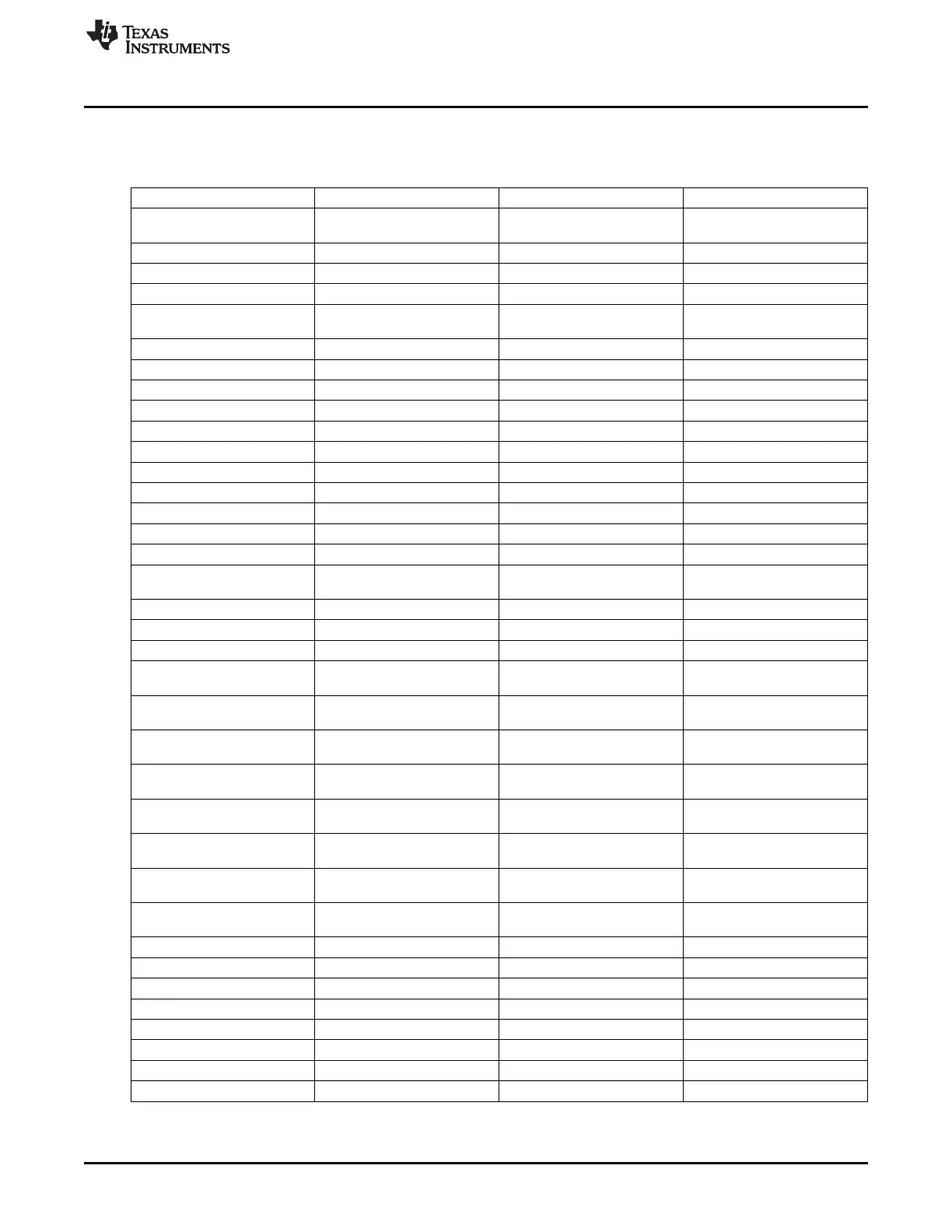

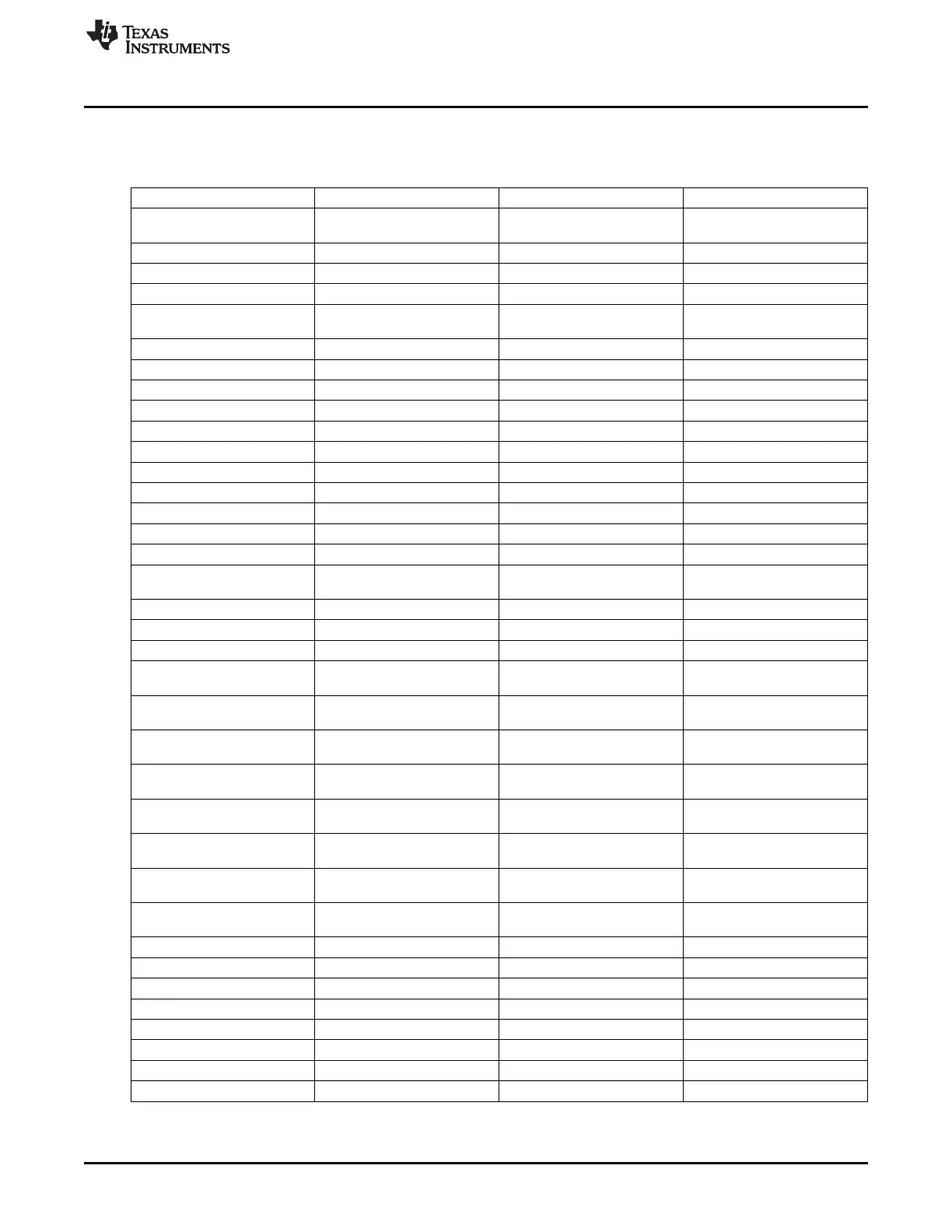

Table 6-1. ARM Cortex-A8 Interrupts

Int Number Acronym/name Source Signal Name

0 EMUINT MPU Subsystem Internal Emulation interrupt

(EMUICINTR)

1 COMMTX MPU Subsystem Internal CortexA8 COMMTX

2 COMMRX MPU Subsystem Internal CortexA8 COMMRX

3 BENCH MPU Subsystem Internal CortexA8 NPMUIRQ

4 ELM_IRQ ELM Sinterrupt (Error location

process completion)

5 Reserved

6 Reserved

7 NMI External Pin (active low)

(1)

nmi_int

8 Reserved

9 L3DEBUG L3 l3_FlagMux_top_FlagOut1

10 L3APPINT L3 l3_FlagMux_top_FlagOut0

11 PRCMINT PRCM irq_mpu

12 EDMACOMPINT TPCC (EDMA) tpcc_int_pend_po0

13 EDMAMPERR TPCC (EDMA) tpcc_mpint_pend_po

14 EDMAERRINT TPCC (EDMA) tpcc_errint_pend_po

15 Reserved

16 ADC_TSC_GENINT ADC_TSC (Touchscreen gen_intr_pend

Controller)

17 USBSSINT USBSS usbss_intr_pend

18 USBINT0 USBSS usb0_intr_pend

19 USBINT1 USBSS usb1_intr_pend

20 PRU_ICSS_EVTOUT0 pr1_host[0] output/events pr1_host_intr0_intr_pend

exported from PRU-ICSS

(2)

21 PRU_ICSS_EVTOUT1 pr1_host[1] output/events pr1_host_intr1_intr_pend

exported from PRU-ICSS

(2)

22 PRU_ICSS_EVTOUT2 pr1_host[2] output/events pr1_host_intr2_intr_pend

exported from PRU-ICSS

(2)

23 PRU_ICSS_EVTOUT3 pr1_host[3] output/events pr1_host_intr3_intr_pend

exported from PRU-ICSS

(2)

24 PRU_ICSS_EVTOUT4 pr1_host[4] output/events pr1_host_intr4_intr_pend

exported from PRU-ICSS

(2)

25 PRU_ICSS_EVTOUT5 pr1_host[5] output/events pr1_host_intr5_intr_pend

exported from PRU-ICSS

(2)

26 PRU_ICSS_EVTOUT6 pr1_host[6] output/events pr1_host_intr6_intr_pend

exported from PRU-ICSS

(2)

27 PRU_ICSS_EVTOUT7 pr1_host[7] output/events pr1_host_intr7_intr_pend

exported from PRU-ICSS

(2)

28 MMCSD1INT MMCSD1 SINTERRUPTN

29 MMCSD2INT MMCSD2 SINTERRUPTN

30 I2C2INT I2C2 POINTRPEND

31 eCAP0INT eCAP0 event/interrupt ecap_intr_intr_pend

32 GPIOINT2A GPIO 2 POINTRPEND1

33 GPIOINT2B GPIO 2 POINTRPEND2

34 USBWAKEUP USBSS slv0p_Swakeup

35 Reserved

(1)

For differences in operation based on AM335x silicon revisions, see Section 1.2, Silicon Revision Functional Differences and

Enhancements.

(2)

pr1_host_intr[0:7] corresponds to Host-2 to Host-9 of the PRU-ICSS interrupt controller.

199

SPRUH73H–October 2011–Revised April 2013 Interrupts

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...