EDMA3 Registers

www.ti.com

11.4.1.5.4 Memory Protection Page Attribute Register (MPPAn)

The memory protection page attribute register (MPPAn) is shown in Figure 11-69 and described in

Table 11-53.

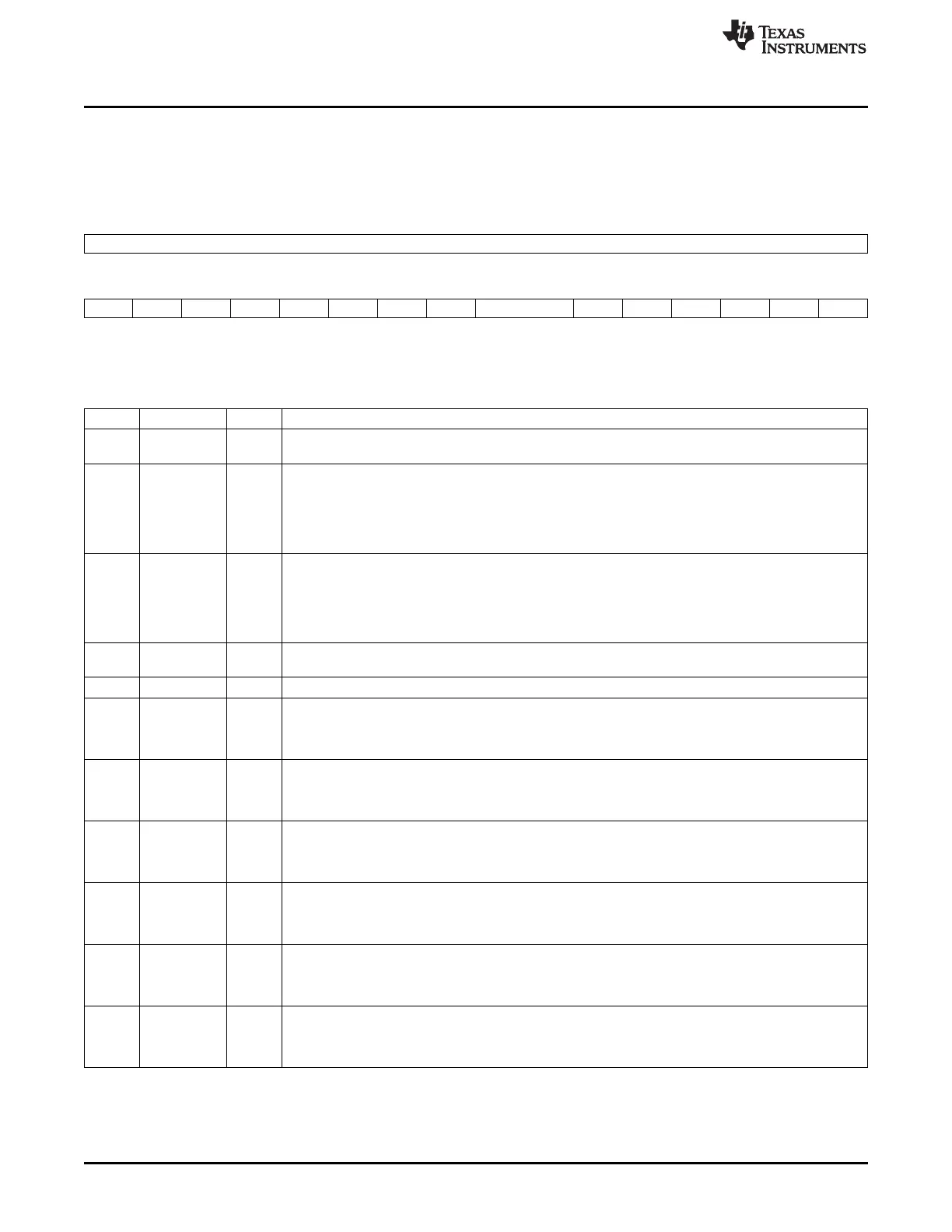

Figure 11-69. Memory Protection Page Attribute Register (MPPAn)

31 16

Reserved

R-0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AID5 AID4 AID3 AID2 AID1 AID0 EXT Rsvd Reserved SR SW SX UR UW UX

RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 R-0 RW-1 RW-1 RW-1 RW-0 RW-1 RW-1 RW-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

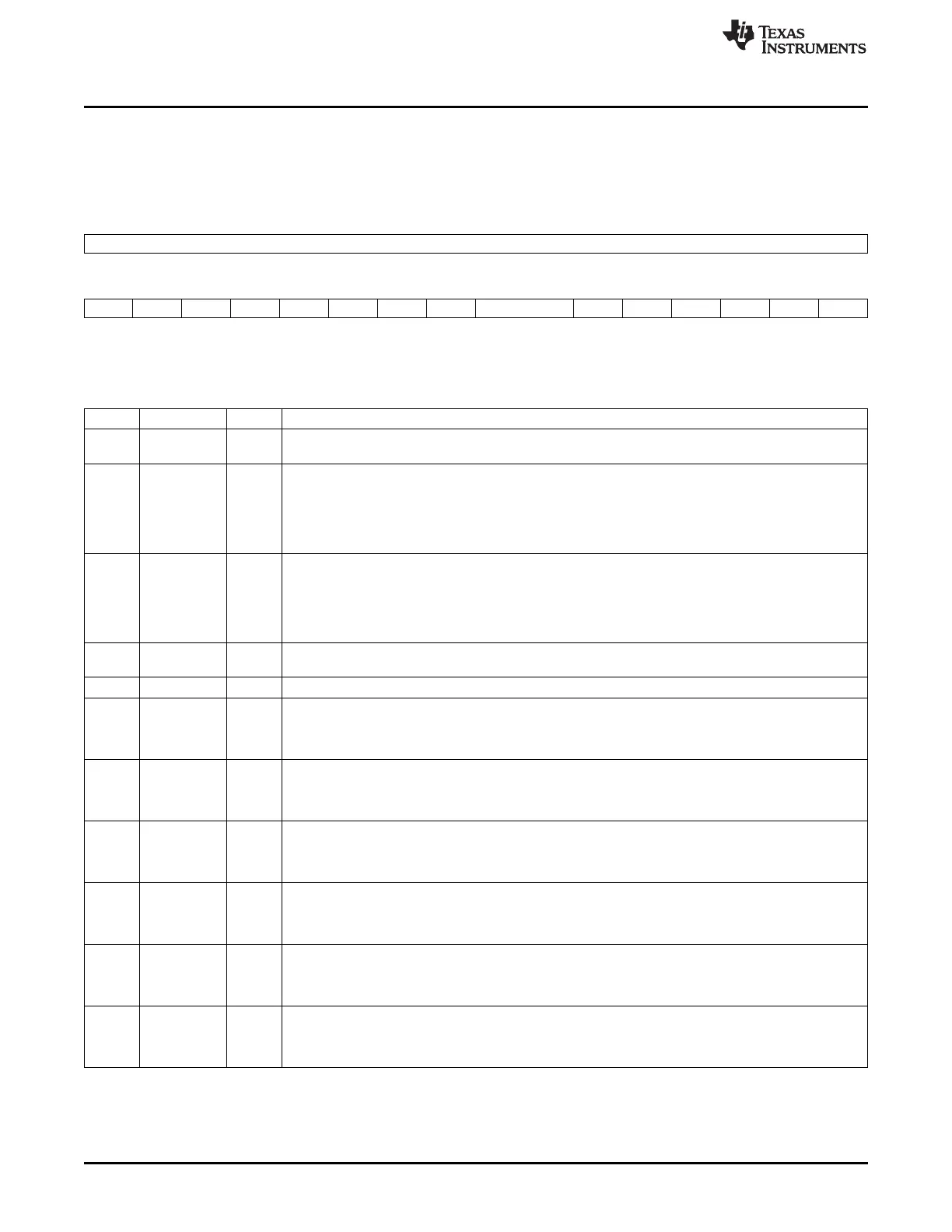

Table 11-53. Memory Protection Page Attribute Register (MPPAn) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

15-10 AIDm Allowed ID 'N'

0 Requests with Privilege ID == N are not allowed to region M, regardless of permission settings (UW,

UR, SW, SR).

1 Requests with Privilege ID == N are permitted, if access type is allowed as defined by permission

settings (UW, UR, SW, SR).

9 EXT External Allowed ID.

0 Requests with Privilege ID >= 6 are not allowed to region M, regardless of permission settings (UW,

UR, SW, SR).

1 Requests with Privilege ID >= 6 are permitted, if access type is allowed as defined by permission

settings (UW, UR, SW, SR).

8 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

7-6 Reserved 1 Reserved. Always write 1 to this bit.

5 SR Supervisor read permission.

0 Supervisor read accesses are not allowed from region M.

1 Supervisor write accesses are allowed from region M addresses.

4 SW Supervisor write permission.

0 Supervisor write accesses are not allowed to region M.

1 Supervisor write accesses are allowed to region N addresses.

3 SX Supervisor execute permission.

0 Supervisor execute accesses are not allowed from region M.

1 Supervisor execute accesses are allowed from region M addresses.

2 UR User read permission.

0 User read accesses are not allowed from region M.

1 User read accesses are allowed from region N addresses.

1 UW User write permission.

0 User write accesses are not allowed to region M.

1 User write accesses are allowed to region M addresses.

0 UX User execute permission.

0 User execute accesses are not allowed from region M.

1 User execute accesses are allowed from region M addresses.

968

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...