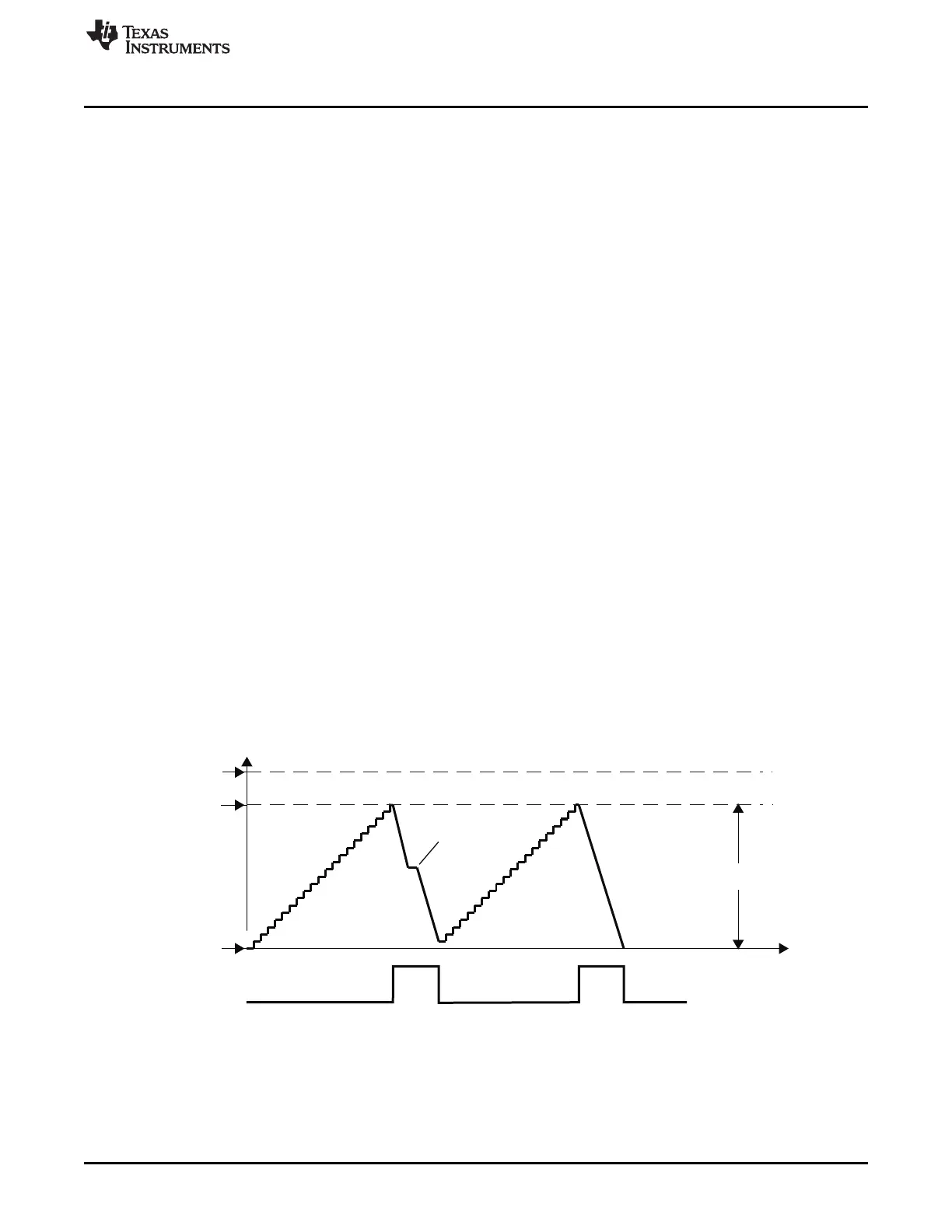

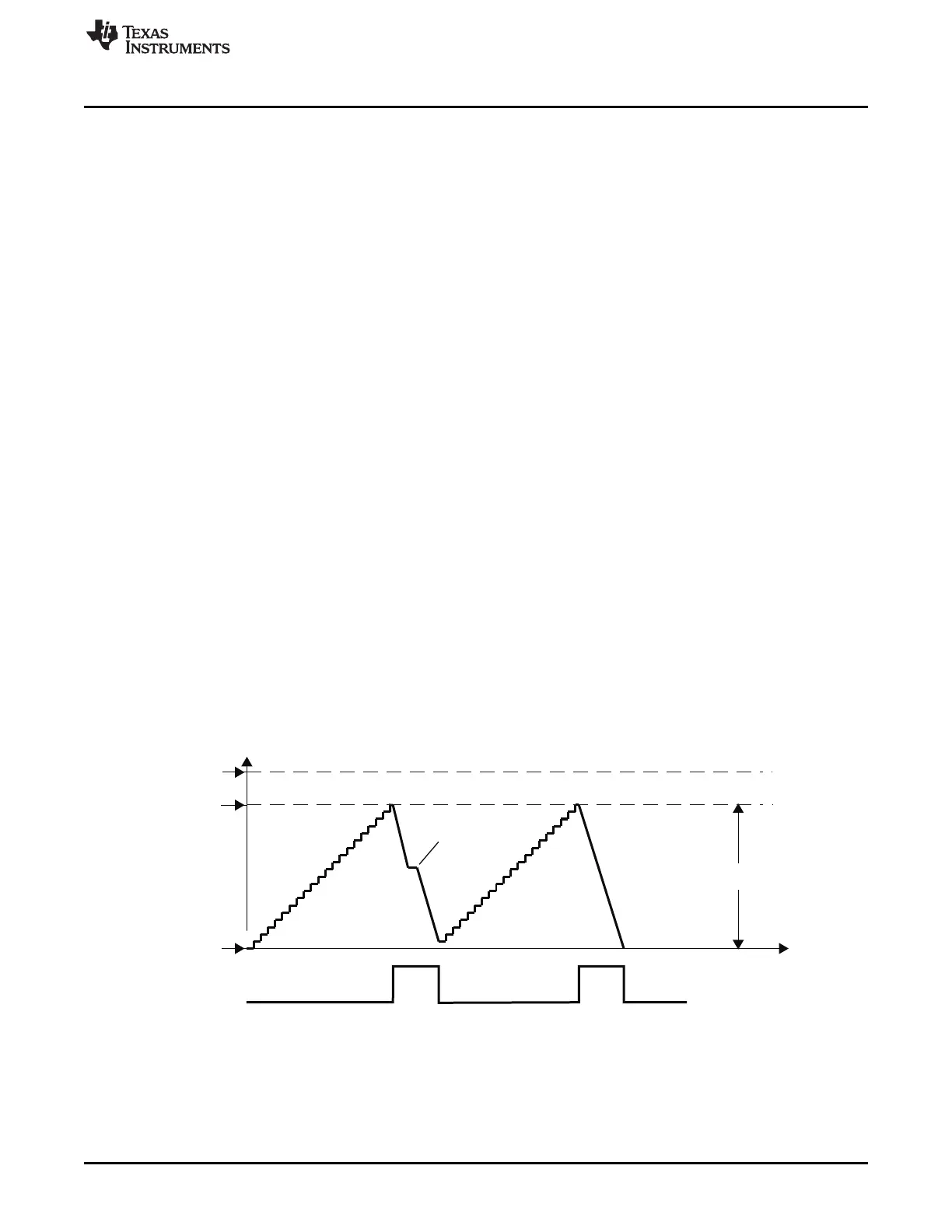

RX buffer

maximum

Zero level

Programmable

threshold

32 characters

Time

Data received while DMA

operation ongoing

DMA active periods; this

does not represent the DMA

signaling.

uart-026

www.ti.com

Functional Description

These signals can be selected as follows:

• When the UARTi.UART_SCR[0] DMA_MODE_CTL bit is set to 0, setting the

UARTi.UART_FCR[3]DMA_MODE bit to 0 enables DMA mode 0. Setting the DMA_MODE bit to 1

enables DMA mode 1.

• When the DMA_MODE_CTL bit is set to 1, the UARTi.UART_SCR[2:1]DMA_MODE_2 bit field

determines DMA mode 0 to mode 3 based on the supplementary control register (UART_SCR)

description.

For example:

• If no DMA operation is desired, set the DMA_MODE_CTL bit to 1 and the DMA_MODE_2 bit field to

0x0. (The DMA_MODE bit is discarded.)

• If DMA mode 1 is desired, set the DMA_MODE_CTL bit to 0 and the DMA_MODE bit to 1, or set the

DMA_MODE_CTL bit to 1 and the DMA_MODE_2 bit field to 01. (The DMA_MODE bit is discarded.)

If the FIFOs are disabled (the UARTi.UART_FCR[0] FIFO_EN bit is set to 0), the DMA occurs in single-

character transfers.

When DMA mode 0 is programmed, the signals associated with DMA operation are not active.

Depending on UART_MDR3[2] SET_DMA_TX_THRESHOLD, the threshold can be programmed different

ways:

• SET_TX_DMA_THRESHOLD = 1:

The threshold value will be the value of the UART_TX_DMA_THRESHOLD register. If

SET_TX_DMA_THRESHOLD + TX trigger spaces 64, then the default method of threshold is used:

threshold value = TX FIFO size.

• SET_TX_DMA_THRESHOLD = 0:

The threshold value = TX FIFO size - TX trigger space. The TX DMA line is asserted if the TX FIFO

level is lower then the threshold. It remains asserted until TX trigger spaces number of bytes are

written into the FIFO. The DMA line is then deasserted and the FIFO level is compared with the

threshold value.

19.3.6.4.1 DMA Transfers (DMA Mode 1, 2, or 3)

Figure 19-7 through Figure 19-10 show the supported DMA operations.

Figure 19-7. Receive FIFO DMA Request Generation (32 Characters)

In receive mode, a DMA request is generated when the RX FIFO reaches its threshold level defined in the

trigger level register (UARTi.UART_TLR). This request is deasserted when the number of bytes defined by

the threshold level is read by the sDMA.

3463

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...