GPIO Registers

www.ti.com

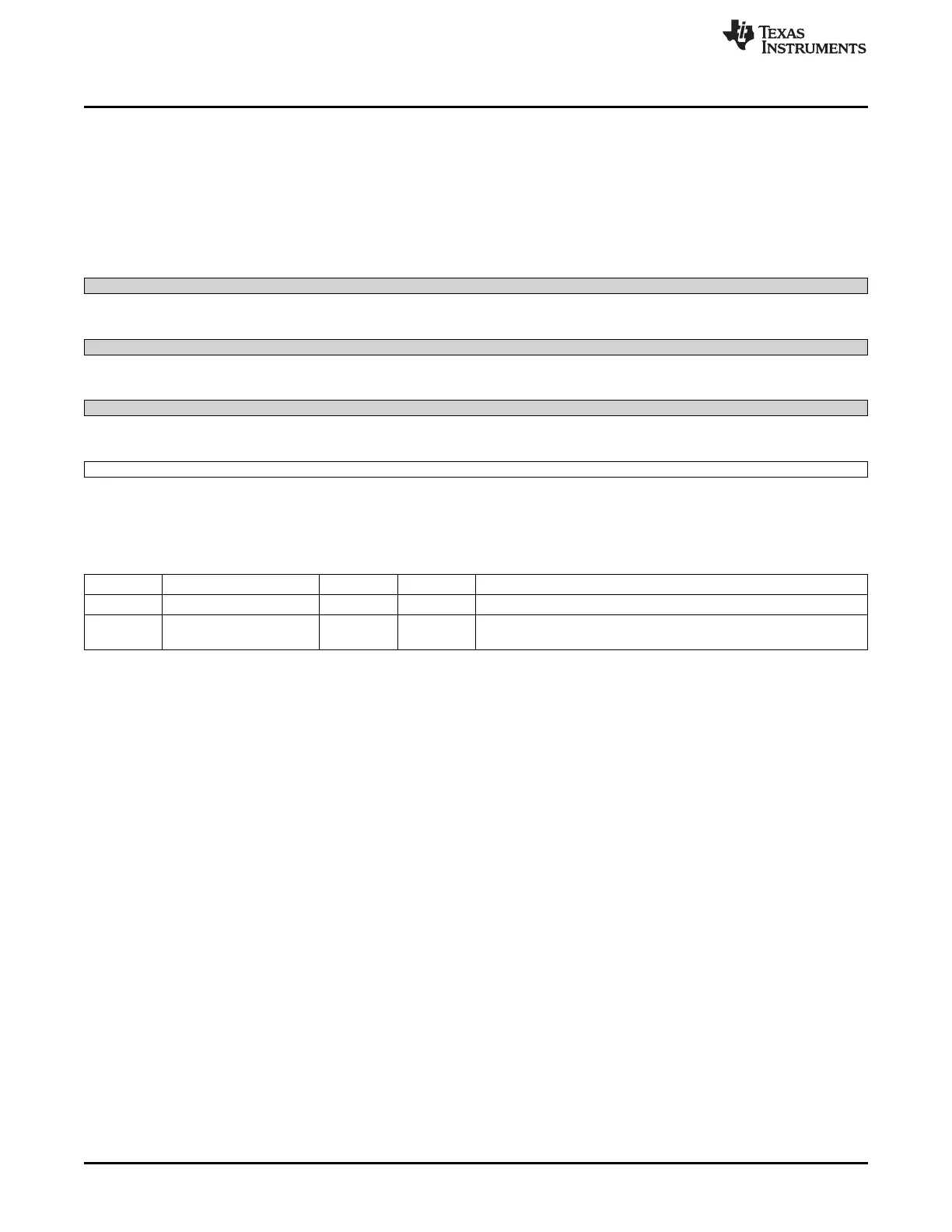

25.4.1.24 GPIO_DEBOUNCINGTIME Register (offset = 154h) [reset = 0h]

GPIO_DEBOUNCINGTIME is shown in Figure 25-30 and described in Table 25-29.

The GPIO_DEBOUNCINGTIME register controls debouncing time (the value is global for all ports). The

debouncing cell is running with the debouncing clock (32 kHz), this register represents the number of the

clock cycle(s) (31 s long) to be used.

Figure 25-30. GPIO_DEBOUNCINGTIME Register

31 30 29 28 27 26 25 24

Reserved

R/W-0h

23 22 21 20 19 18 17 16

Reserved

R/W-0h

15 14 13 12 11 10 9 8

Reserved

R/W-0h

7 6 5 4 3 2 1 0

DEBOUNCETIME

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

Table 25-29. GPIO_DEBOUNCINGTIME Register Field Descriptions

Bit Field Type Reset Description

31-8 Reserved R/W 0h

7-0 DEBOUNCETIME R/W 0h Input Debouncing Value in 31 microsecond steps.

Debouncing Value = (DEBOUNCETIME + 1) * 31 microseconds

4092

General-Purpose Input/Output SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...