GPIO Registers

www.ti.com

25.4.1.12 GPIO_IRQWAKEN_0 Register (offset = 44h) [reset = 0h]

GPIO_IRQWAKEN_0 is shown in Figure 25-18 and described in Table 25-17.

Per-event wakeup enable vector (corresponding to first line of interrupt). Every 1-bit field in the

GPIO_IRQWAKEN_0 register enables a specific (synchronous) IRQ request source to generate an

asynchronous wakeup (on the appropriate swakeup line). This register allows the user to mask the

expected transition on input GPIO from generating a wakeup request. The GPIO_IRQWAKEN_0 is

programmed synchronously with the interface clock before any Idle mode request coming from the host

processor. Note: In Force-Idle mode, the module wake-up feature is totally inhibited. The wake-up

generation can also be gated at module level using the EnaWakeUp bit from GPIO_SYSCONFIG register.

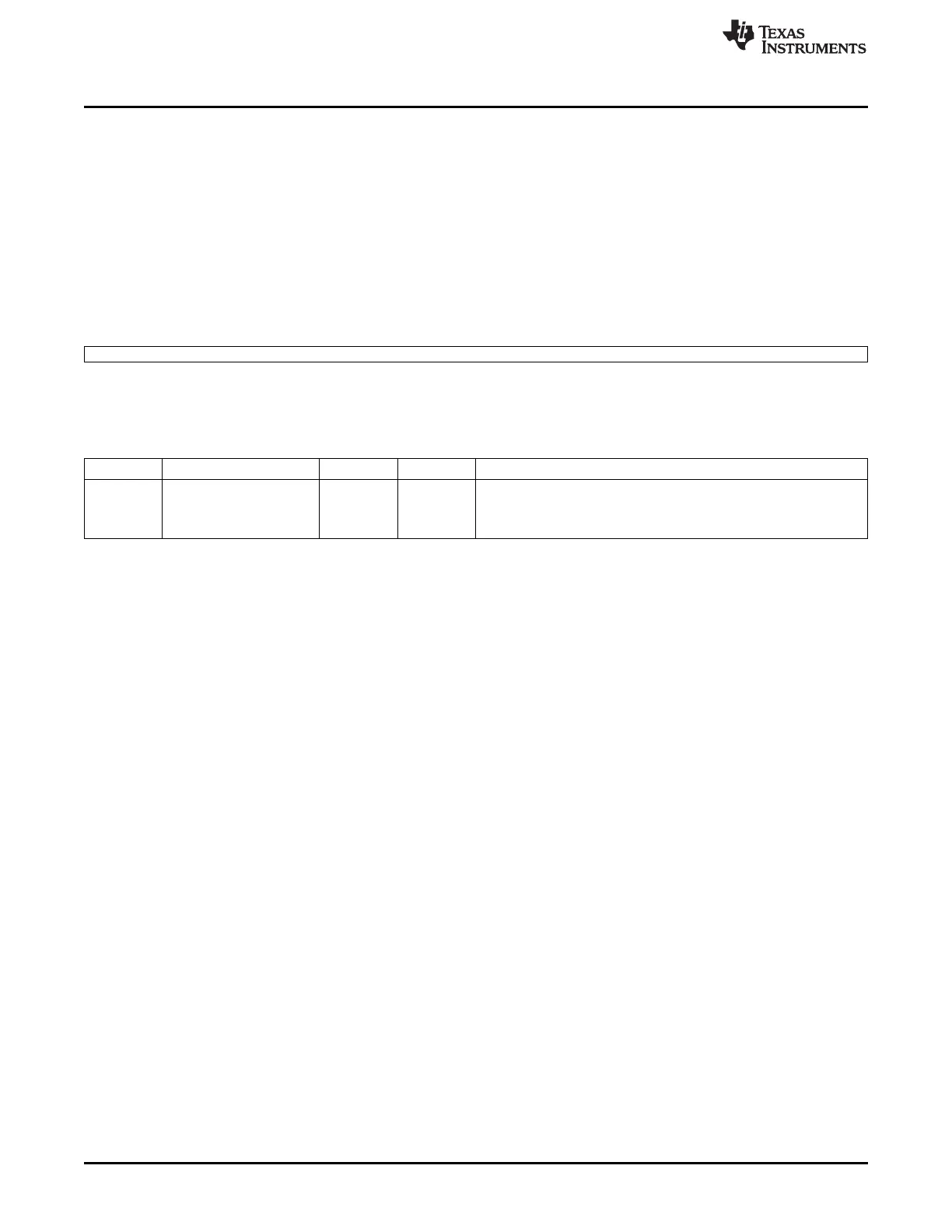

Figure 25-18. GPIO_IRQWAKEN_0 Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

INTLINE

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

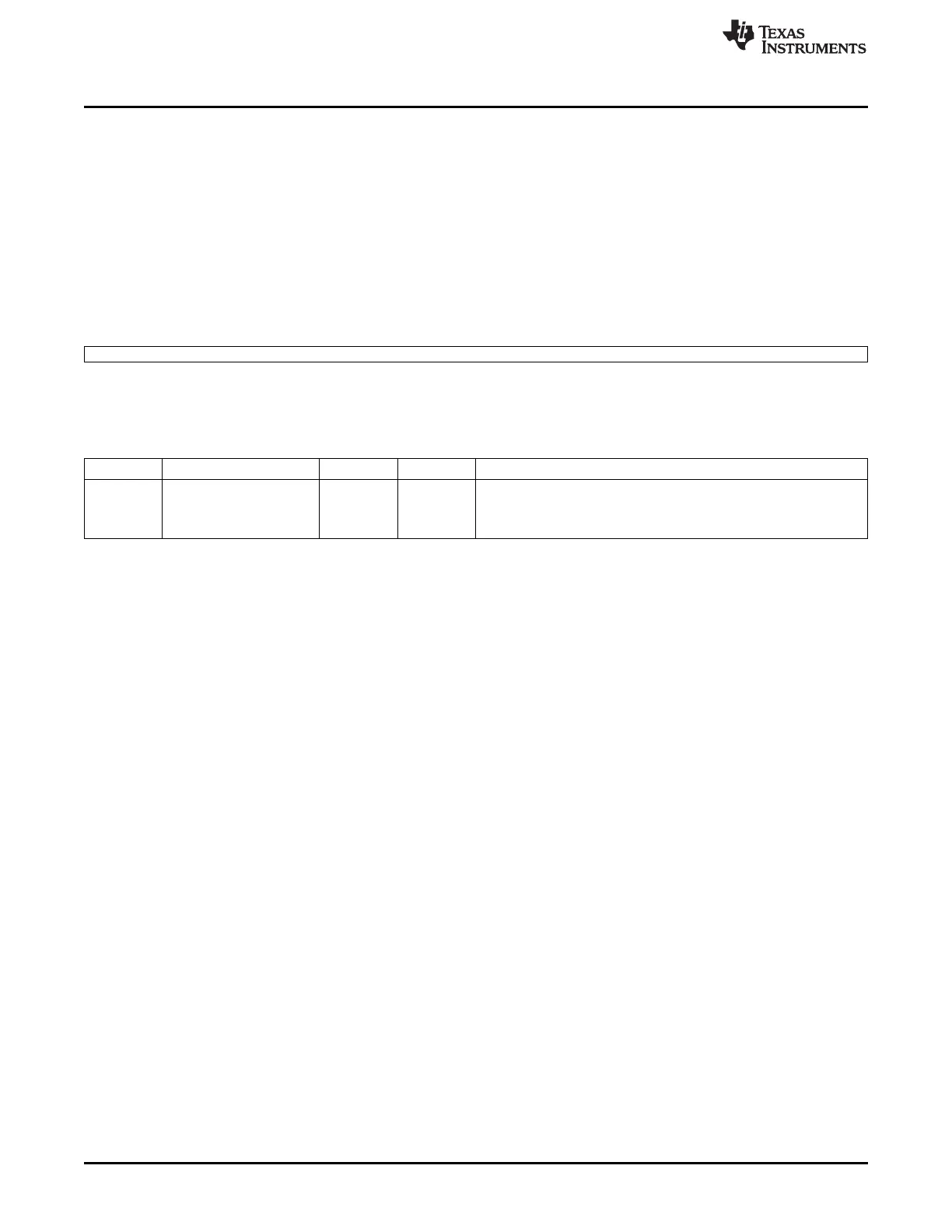

Table 25-17. GPIO_IRQWAKEN_0 Register Field Descriptions

Bit Field Type Reset Description

31-0 INTLINE R/W 0h

Wakeup Enable for Interrupt Line

0x0 = Disable wakeup generation.

0x1 = Enable wakeup generation.

4080

General-Purpose Input/Output SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...