www.ti.com

Functional Description

11.3.3.2 EDMA3 Channel PaRAM Set Entry Fields

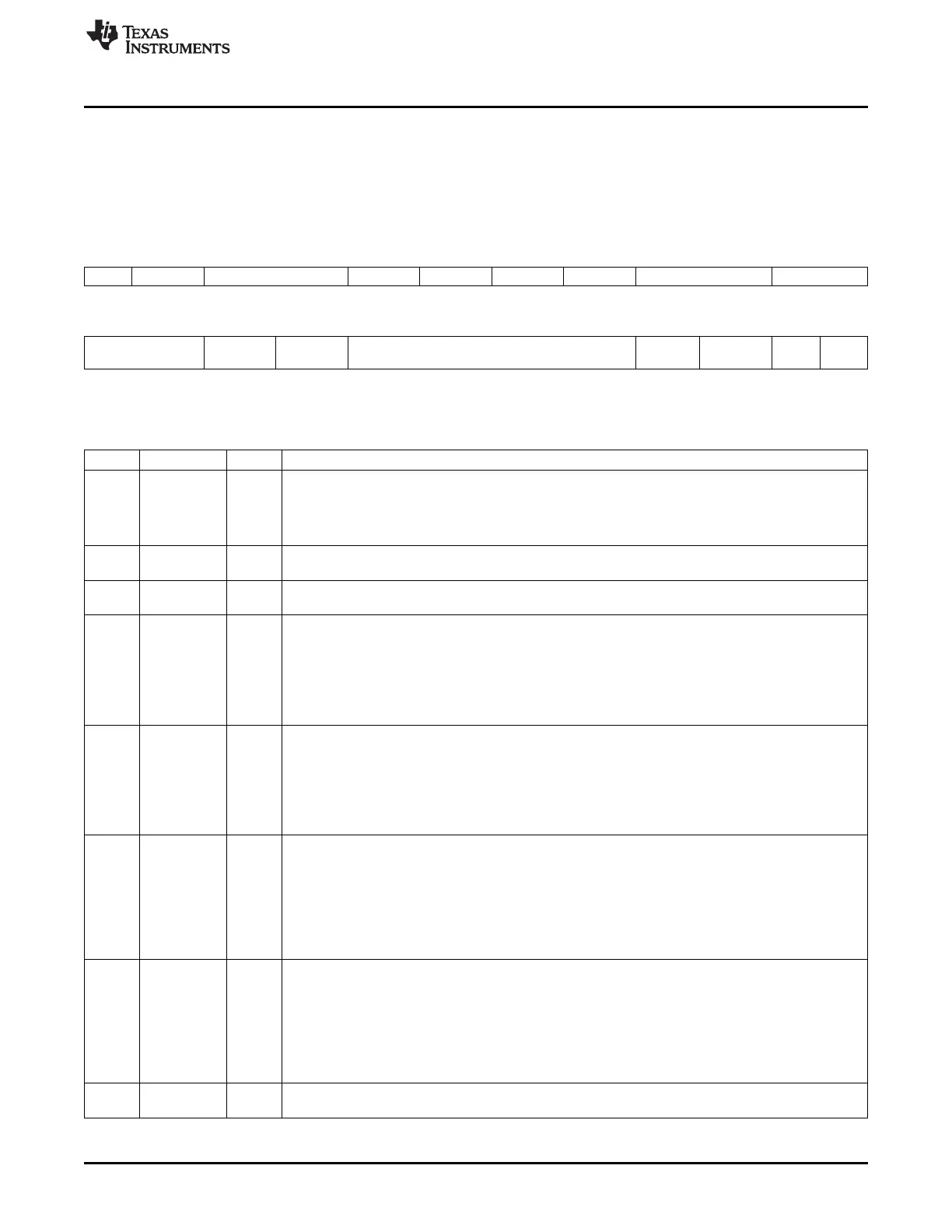

11.3.3.2.1 Channel Options Parameter (OPT)

The channel options parameter (OPT) is shown in Figure 11-10 and described in Table 11-7.

Figure 11-10. Channel Options Parameter (OPT)

31 30 28 27 24 23 22 21 20 19 18 17 16

PRIV Reserved PRIVID ITCCHEN TCCHEN ITCINTEN TCINTEN Reserved TCC

R-0 R-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

15 12 11 10 8 7 4 3 2 1 0

TCC TCCMOD FWID Reserved STATIC SYNCDIM DAM SAM

E

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

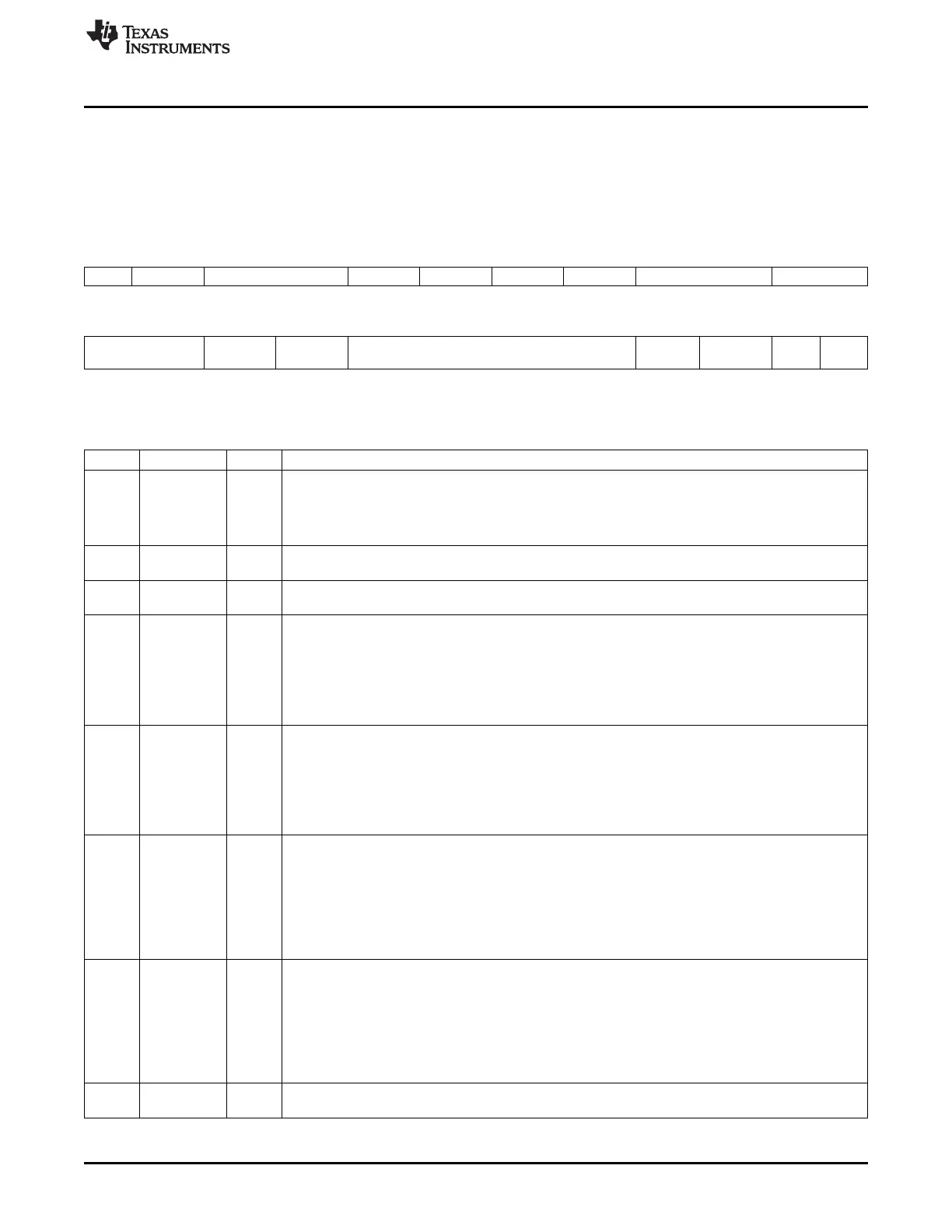

Table 11-7. Channel Options Parameters (OPT) Field Descriptions

Bit Field Value Description

31 PRIV Privilege level (supervisor versus user) for the host/CPU/DMA that programmed this PaRAM set. This

value is set with the EDMA3 master’s privilege value when any part of the PaRAM set is written.

0 User level privilege.

1 Supervisor level privilege.

30-28 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

27-24 PRIVID 0-Fh Privilege identification for the external host/CPU/DMA that programmed this PaRAM set. This value is

set with the EDMA3 master’s privilege identification value when any part of the PaRAM set is written.

23 ITCCHEN Intermediate transfer completion chaining enable.

0 Intermediate transfer complete chaining is disabled.

1 Intermediate transfer complete chaining is enabled.

When enabled, the chained event register (CER/CERH) bit is set on every intermediate chained transfer

completion (upon completion of every intermediate TR in the PaRAM set, except the final TR in the

PaRAM set). The bit (position) set in CER or CERH is the TCC value specified.

22 TCCHEN Transfer complete chaining enable.

0 Transfer complete chaining is disabled.

1 Transfer complete chaining is enabled.

When enabled, the chained event register (CER/CERH) bit is set on final chained transfer completion

(upon completion of the final TR in the PaRAM set). The bit (position) set in CER or CERH is the TCC

value specified.

21 ITCINTEN Intermediate transfer completion interrupt enable.

0 Intermediate transfer complete interrupt is disabled.

1 Intermediate transfer complete interrupt is enabled.

When enabled, the interrupt pending register (IPR / IPRH) bit is set on every intermediate transfer

completion (upon completion of every intermediate TR in the PaRAM set, except the final TR in the

PaRAM set). The bit (position) set in IPR or IPRH is the TCC value specified. To generate a completion

interrupt to the CPU, the corresponding IER [TCC] / IERH [TCC] bit must be set.

20 TCINTEN Transfer complete interrupt enable.

0 Transfer complete interrupt is disabled.

1 Transfer complete interrupt is enabled.

When enabled, the interrupt pending register (IPR / IPRH) bit is set on transfer completion (upon

completion of the final TR in the PaRAM set). The bit (position) set in IPR or IPRH is the TCC value

specified. To generate a completion interrupt to the CPU, the corresponding IER[TCC] / IERH [TCC] bit

must be set.

19-18 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

885

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...