www.ti.com

Power, Reset, and Clock Management

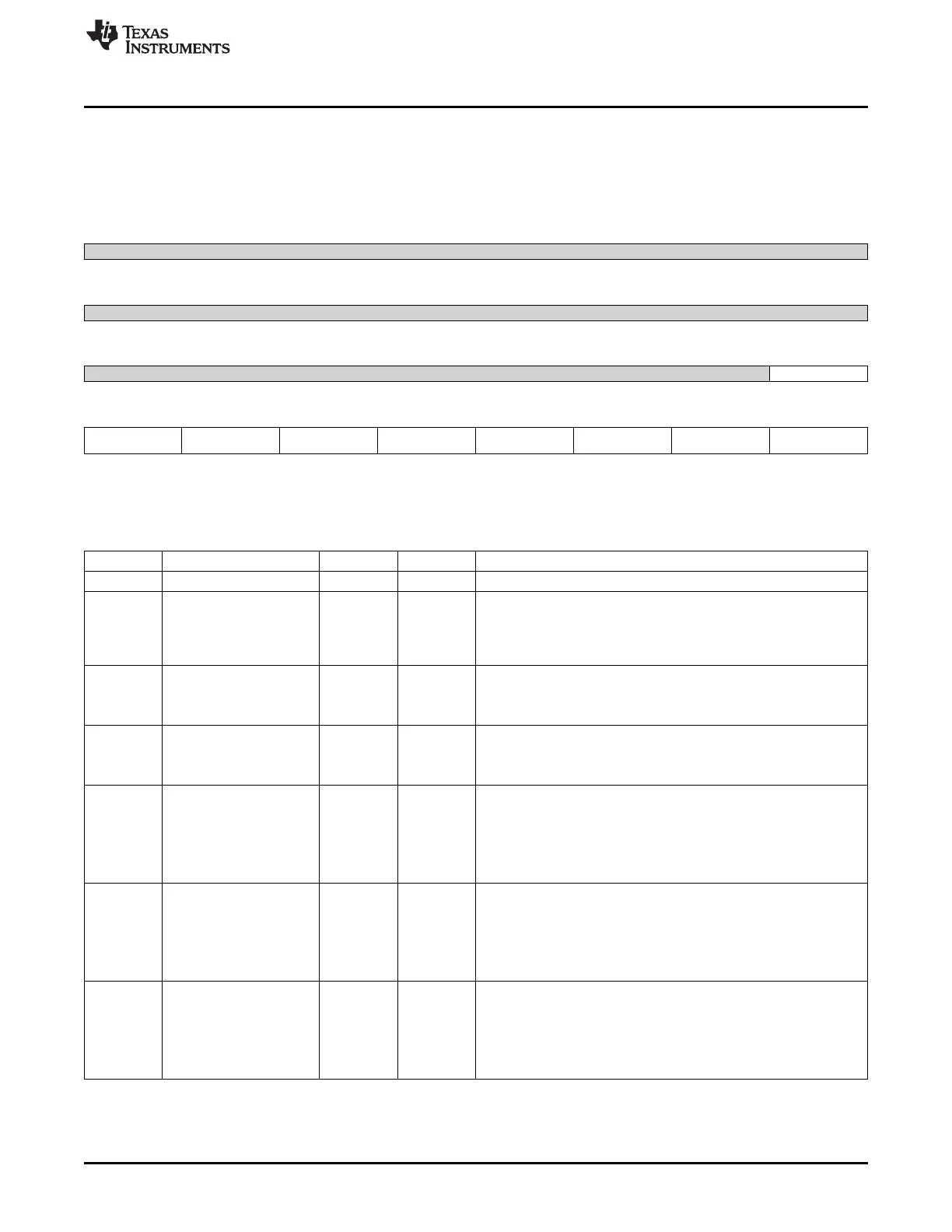

8.1.13.5.7 PRM_LDO_SRAM_MPU_SETUP Register (offset = 18h) [reset = 0h]

PRM_LDO_SRAM_MPU_SETUP is shown in Figure 8-185 and described in Table 8-204.

Setup of the SRAM LDO for MPU voltage domain. [warm reset insensitive]

Figure 8-185. PRM_LDO_SRAM_MPU_SETUP Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved AIPOFF

R-0h R/W-0h

7 6 5 4 3 2 1 0

ENFUNC5 ENFUNC4 ENFUNC3_EXPORT ENFUNC2_EXPORT ENFUNC1_EXPORT ABBOFF_SLEEP_EX ABBOFF_ACT_EXPO DISABLE_RTA_EXP

PORT RT ORT

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

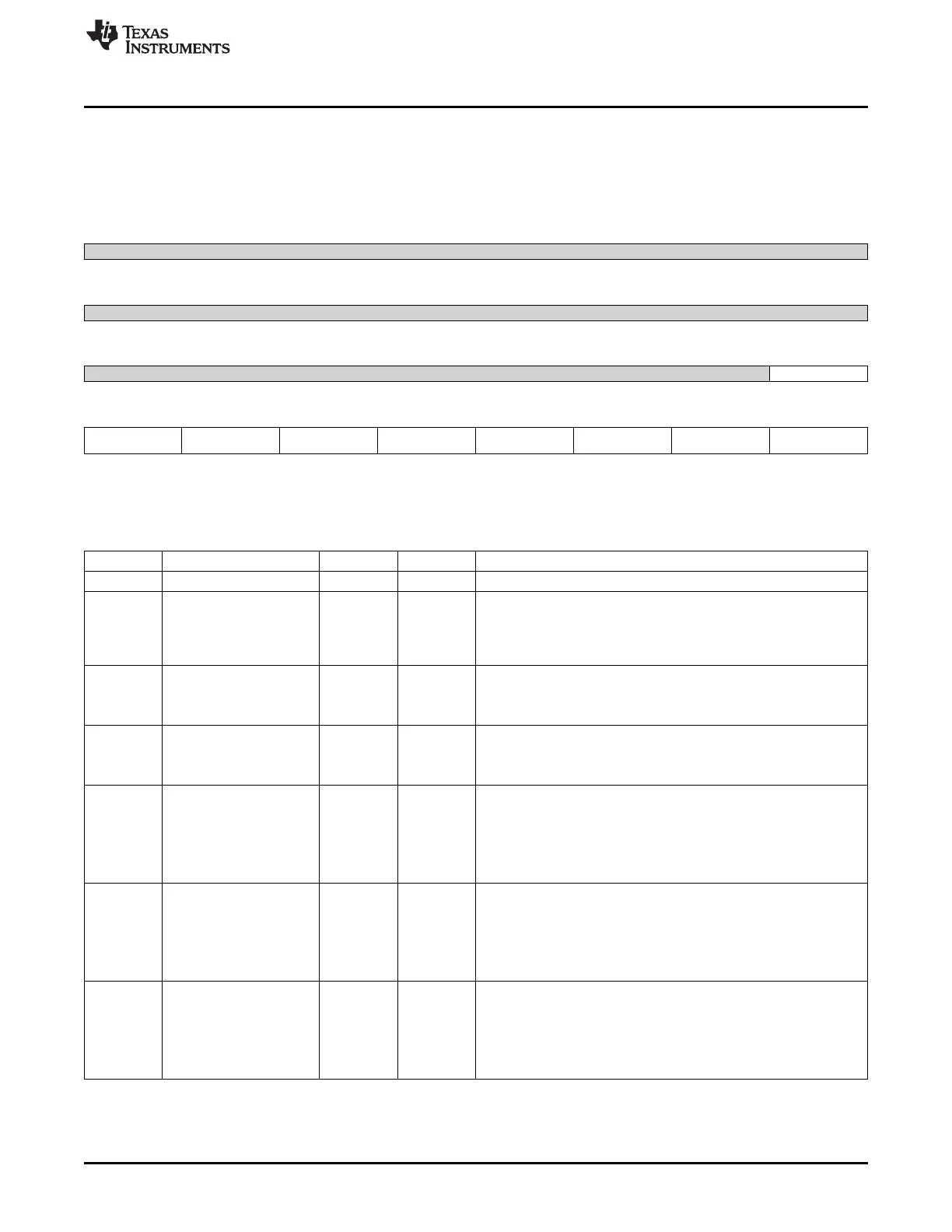

Table 8-204. PRM_LDO_SRAM_MPU_SETUP Register Field Descriptions

Bit Field Type Reset Description

31-9 Reserved R 0h

8 AIPOFF R/W 0h

Override on AIPOFF input of SRAM LDO.

0x0 = No_Override : AIPOFF signal is not overriden

0x1 = Override : AIPOFF signal is overriden to '1'. Corresponding

SRAM LDO is disabled and in HZ mode.

7 ENFUNC5 R/W 0h

ENFUNC5 input of SRAM LDO.

0x0 = One_step : Active to retention is a one step transfer

0x1 = Two_step : Active to retention is a two steps transfer

6 ENFUNC4 R/W 0h

ENFUNC4 input of SRAM LDO.

0x0 = Ext_clock : One external clock is supplied

0x1 = No_ext_clock : No external clock is supplied

5 ENFUNC3_EXPORT R/W 0h ENFUNC3 input of SRAM LDO.

After PowerOn reset and Efuse sensing, this bitfield is automatically

loaded with an Efuse value from control module.

Bitfield remains writable after this.

0x0 = Sub_regul_disabled : Sub regulation is disabled

0x1 = Sub_regul_enabled : Sub regulation is enabled

4 ENFUNC2_EXPORT R/W 0h ENFUNC2 input of SRAM LDO.

After PowerOn reset and Efuse sensing, this bitfield is automatically

loaded with an Efuse value from control module.

Bitfield remains writable after this.

0x0 = Ext_cap : External cap is used

0x1 = No_ext_cap : External cap is not used

3 ENFUNC1_EXPORT R/W 0h ENFUNC1 input of SRAM LDO.

After PowerOn reset and Efuse sensing, this bitfield is automatically

loaded with an Efuse value from control module.

Bitfield remains writable after this.

0x0 = Short_prot_disabled : Short circuit protection is disabled

0x1 = Short_prot_enabled : Short circuit protection is enabled

733

SPRUH73H–October 2011–Revised April 2013 Power, Reset, and Clock Management (PRCM)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...