Ethernet Subsystem Registers

www.ti.com

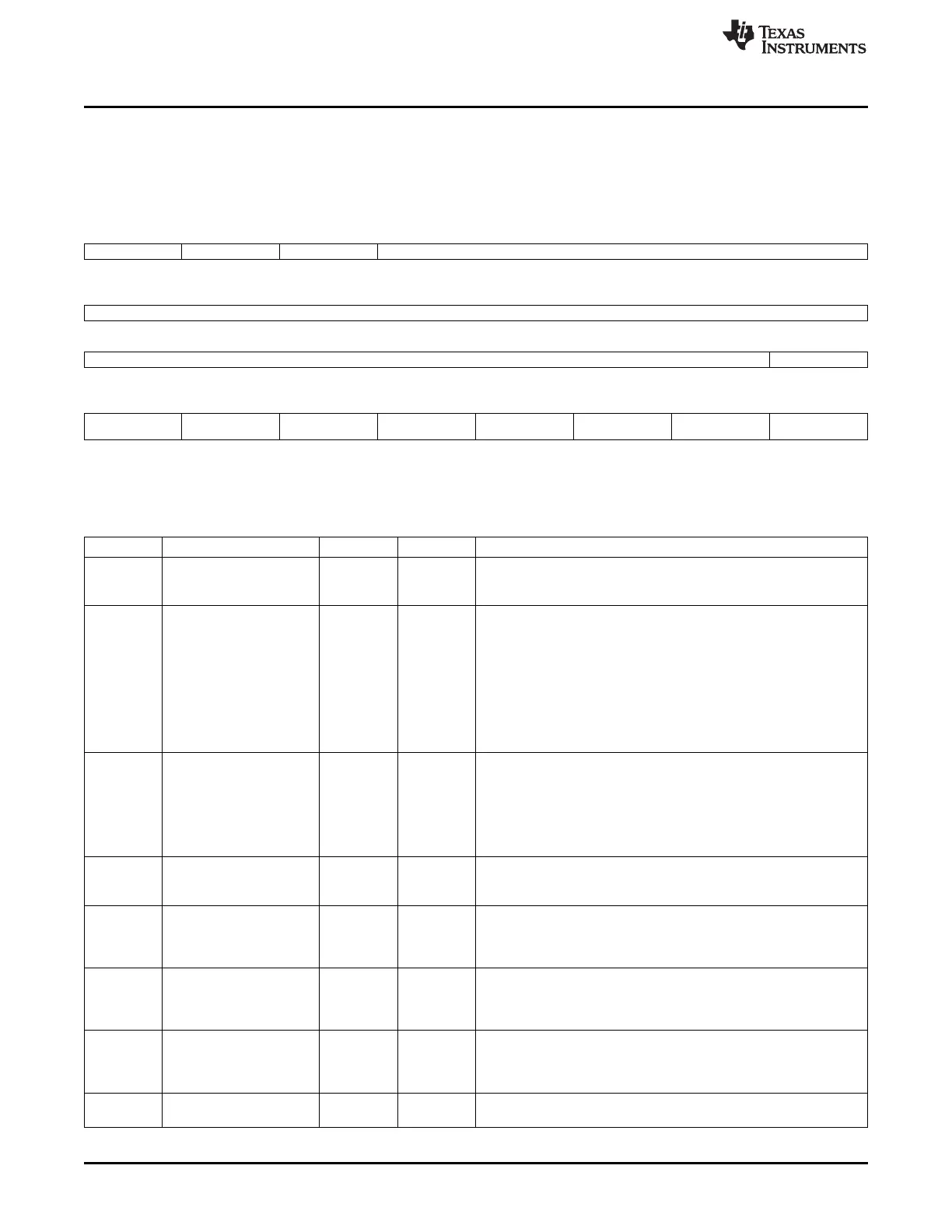

14.5.1.2 CONTROL Register (offset = 8h) [reset = 0h]

CONTROL is shown in Figure 14-16 and described in Table 14-26.

ADDRESS LOOKUP ENGINE CONTROL REGISTER

Figure 14-16. CONTROL Register

31 30 29 28 27 26 25 24

ENABLE_ALE CLEAR_TABLE AGE_OUT_NOW Reserved

R/W-0 R/W-0 R/W-0

23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8

Reserved EN_P0_UNI_FLOOD

R/W-0

7 6 5 4 3 2 1 0

LEARN_NO_VID EN_VID0_MODE ENABLE_OUI_DENY BYPASS RATE_LIMIT_TX VLAN_AWARE ENABLE_AUTH_MO ENABLE_RATE_LIMI

DE T

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

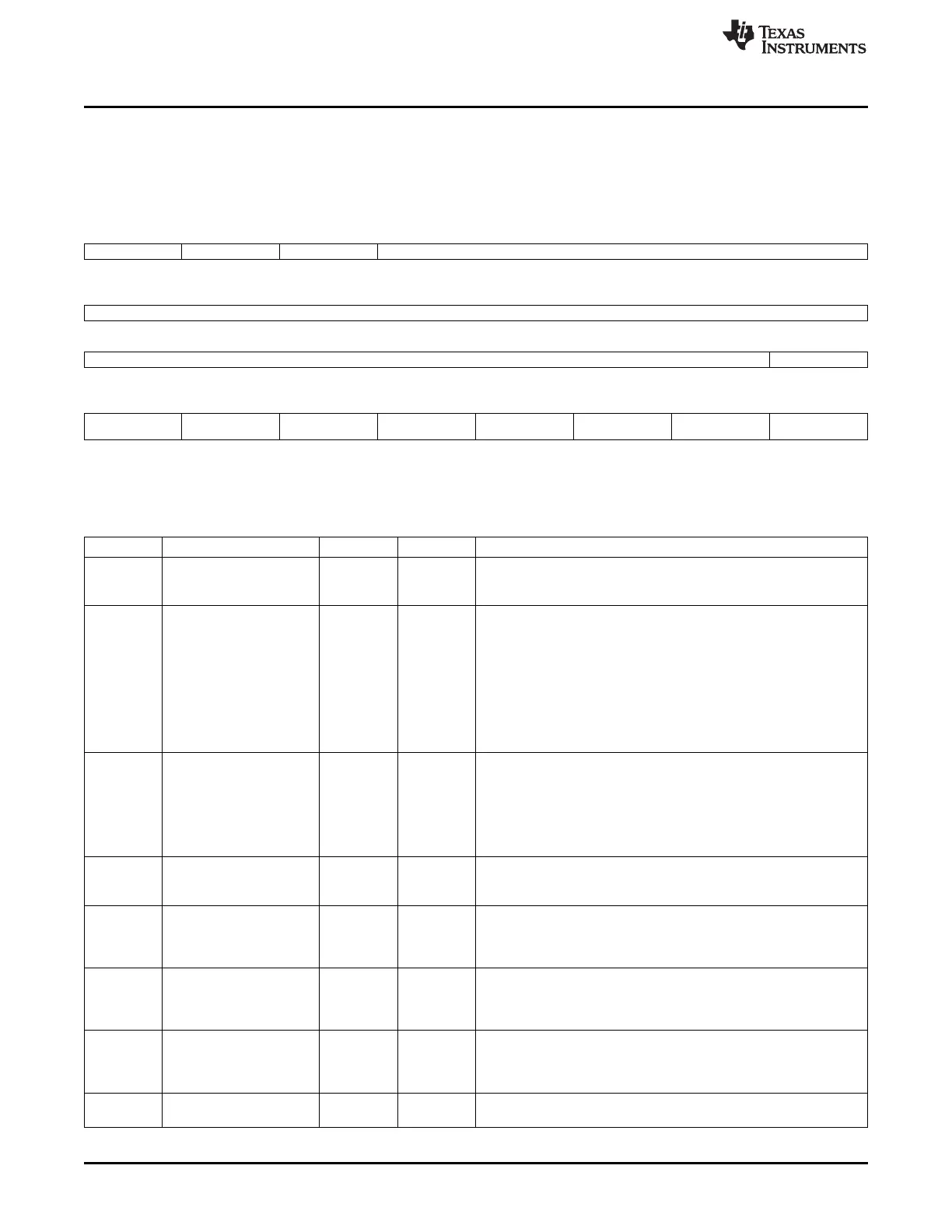

Table 14-26. CONTROL Register Field Descriptions

Bit Field Type Reset Description

31 ENABLE_ALE R/W-0 0 Enable ALE -

0 - Drop all packets

1 - Enable ALE packet processing

30 CLEAR_TABLE R/W-0 0 Clear ALE address table - Setting this bit causes the ALE hardware

to write all table bit values to zero.

Software must perform a clear table operation as part of the ALE

setup/configuration process.

Setting this bit causes all ALE accesses to be held up for 64 clocks

while the clear is performed.

Access to all ALE registers will be blocked (wait states) until the 64

clocks have completed.

This bit cannot be read as one because the read is blocked until the

clear table is completed at which time this bit is cleared to zero.

29 AGE_OUT_NOW R/W-0 0 Age Out Address Table Now - Setting this bit causes the ALE

hardware to remove (free up) any ageable table entry that does not

have a set touch bit.

This bit is cleared when the age out process has completed.

This bit may be read.

The age out process takes 4096 clocks best case (no ale packet

processing during ageout) and 66550 clocks absolute worst case.

8 EN_P0_UNI_FLOOD R/W-0 0 Enable Port 0 (Host Port) unicast flood

0 - do not flood unknown unicast packets to host port (p0)

1 - flood unknown unicast packets to host port (p0)

7 LEARN_NO_VID R/W-0 0 Learn No VID -

0 - VID is learned with the source address

1 - VID is not learned with the source address (source address is not

tied to VID).

6 EN_VID0_MODE R/W-0 0 Enable VLAN ID = 0 Mode

0 - Process the packet with VID = PORT_VLAN[

11:0].

1 - Process the packet with VID = 0.

5 ENABLE_OUI_DENY R/W-0 0 Enable OUI Deny Mode - When set this bit indicates that a packet

with a non OUI table entry matching source address will be dropped

to the host unless the destination address matches a multicast table

entry with the super bit set.

4 BYPASS R/W-0 0 ALE Bypass - When set, all packets received on ports 0 and 1 are

sent to the host (only to the host).

1242

Ethernet Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...