EDMA3 Registers

www.ti.com

11.4.1.1.8 Queue Priority Register (QUEPRI)

The queue priority register (QUEPRI) allows you to change the priority of the individual queues and the

priority of the transfer request (TR) associated with the events queued in the queue. Because the queue to

EDMA3TC mapping is fixed, programming QUEPRI essentially governs the priority of the associated

transfer controller(s) read/write commands with respect to the other bus masters in the device. You can

modify the EDMA3TC priority to obtain the desired system performance.

The QUEPRI is shown in Figure 11-49 and described in Table 11-34.

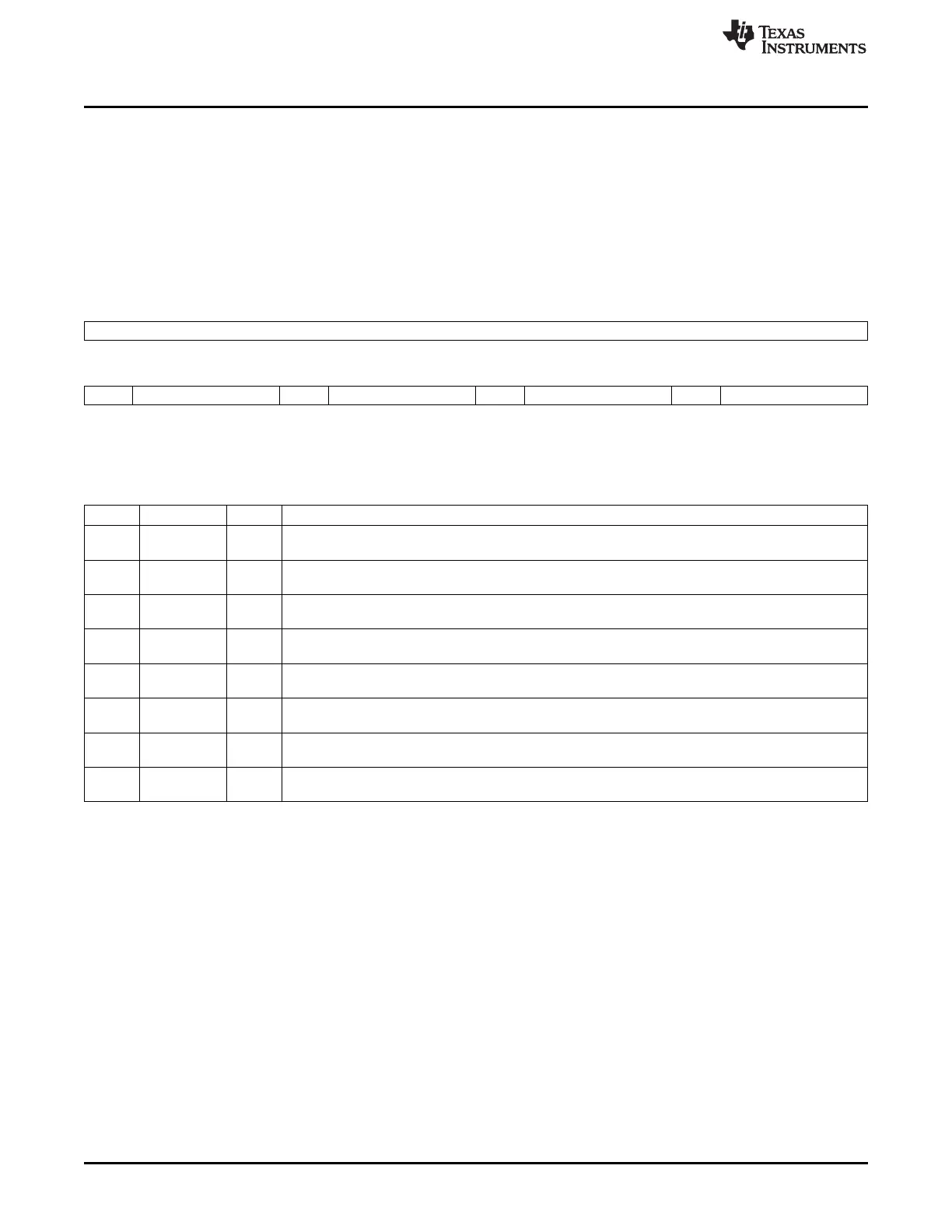

Figure 11-49. Queue Priority Register (QUEPRI)

31 16

Reserved

R-0

15 14 12 11 10 8 7 6 4 3 2 0

Rsvd PRIQ3 Rsvd PRIQ2 Rsvd PRIQ1 Rsvd PRIQ0

R-0 R/W-0 R-0 R/W-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

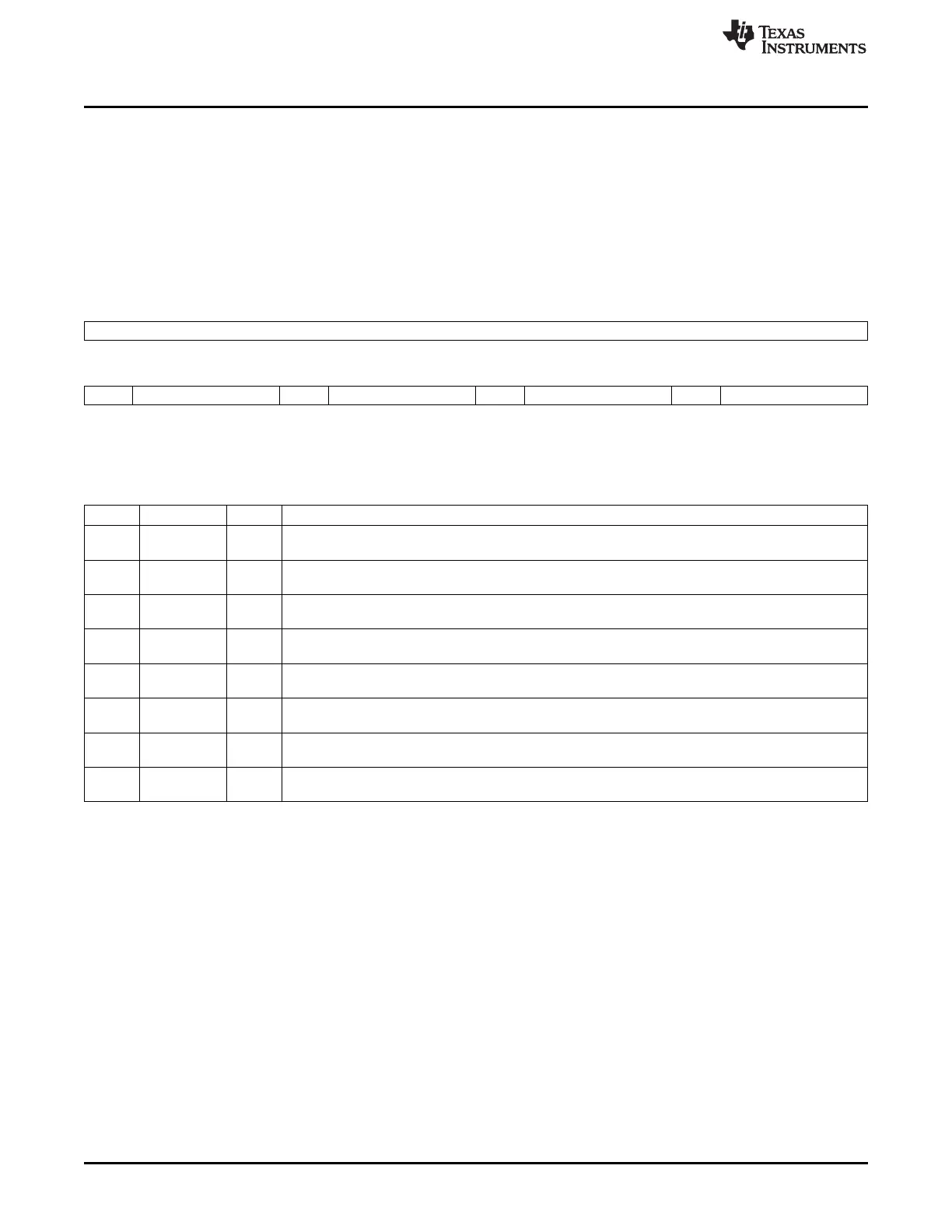

Table 11-34. Queue Priority Register (QUEPRI) Field Descriptions

Bit Field Value Description

31-15 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

14-12 PRIQ3 0-7h Priority level for queue 3. Dictates the priority level used by TC3 relative to other masters in the device.

A value of 0 means highest priority and a value of 7 means lowest priority.

11 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

10-8 PRIQ2 0-7h Priority level for queue 2. Dictates the priority level used by TC2 relative to other masters in the device.

A value of 0 means highest priority and a value of 7 means lowest priority.

7 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

6-4 PRIQ1 0-7h Priority level for queue 1. Dictates the priority level used by TC1 relative to other masters in the device.

A value of 0 means highest priority and a value of 7 means lowest priority.

3 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

2-0 PRIQ0 0-7h Priority level for queue 0. Dictates the priority level used by TC0 relative to other masters in the device.

A value of 0 means highest priority and a value of 7 means lowest priority.

950

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...