Functional Description

www.ti.com

(depending on early or normal completion).

• If both final and intermediate transfer completion chaining (TCCHEN = 1 and ITCCHEN = 1 in OPT)

are enabled, then the chain-trigger event occurs after every transfer request is submitted or completed

(depending on early or normal completion).

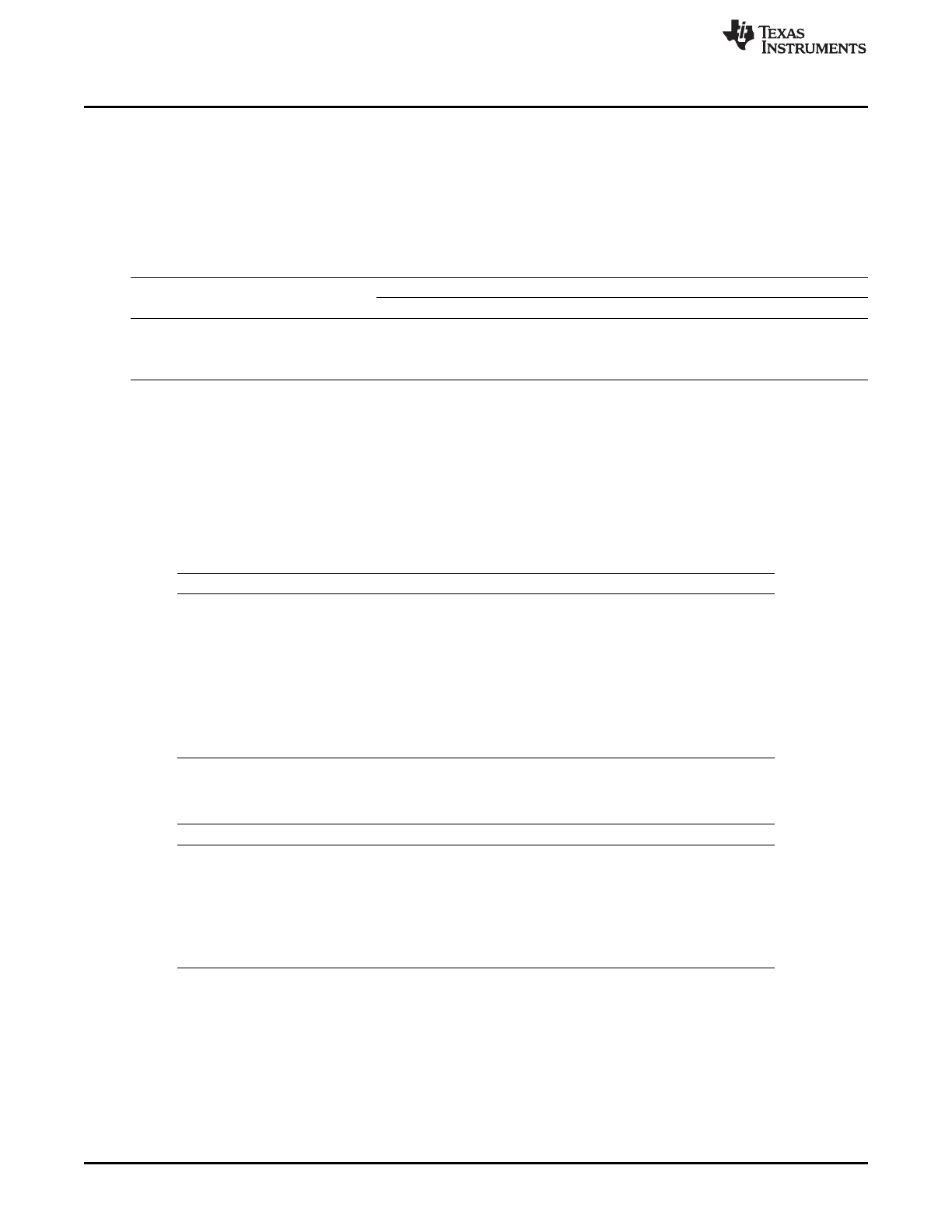

Table 11-12 illustrates the number of chain event triggers occurring in different synchronized scenarios.

Consider channel 31 programmed with ACNT = 3, BCNT = 4, CCNT = 5, and TCC = 30.

Table 11-12. Chain Event Triggers

(Number of chained event triggers on channel 30)

Options A-Synchronized AB-Synchronized

TCCHEN = 1, ITCCHEN = 0 1 (Owing to the last TR) 1 (Owing to the last TR)

TCCHEN = 0, ITCCHEN = 1 19 (Owing to all but the last TR) 4 (Owing to all but the last TR)

TCCHEN = 1, ITCCHEN = 1 20 (Owing to a total of 20 TRs) 5 (Owing to a total of 5 TRs)

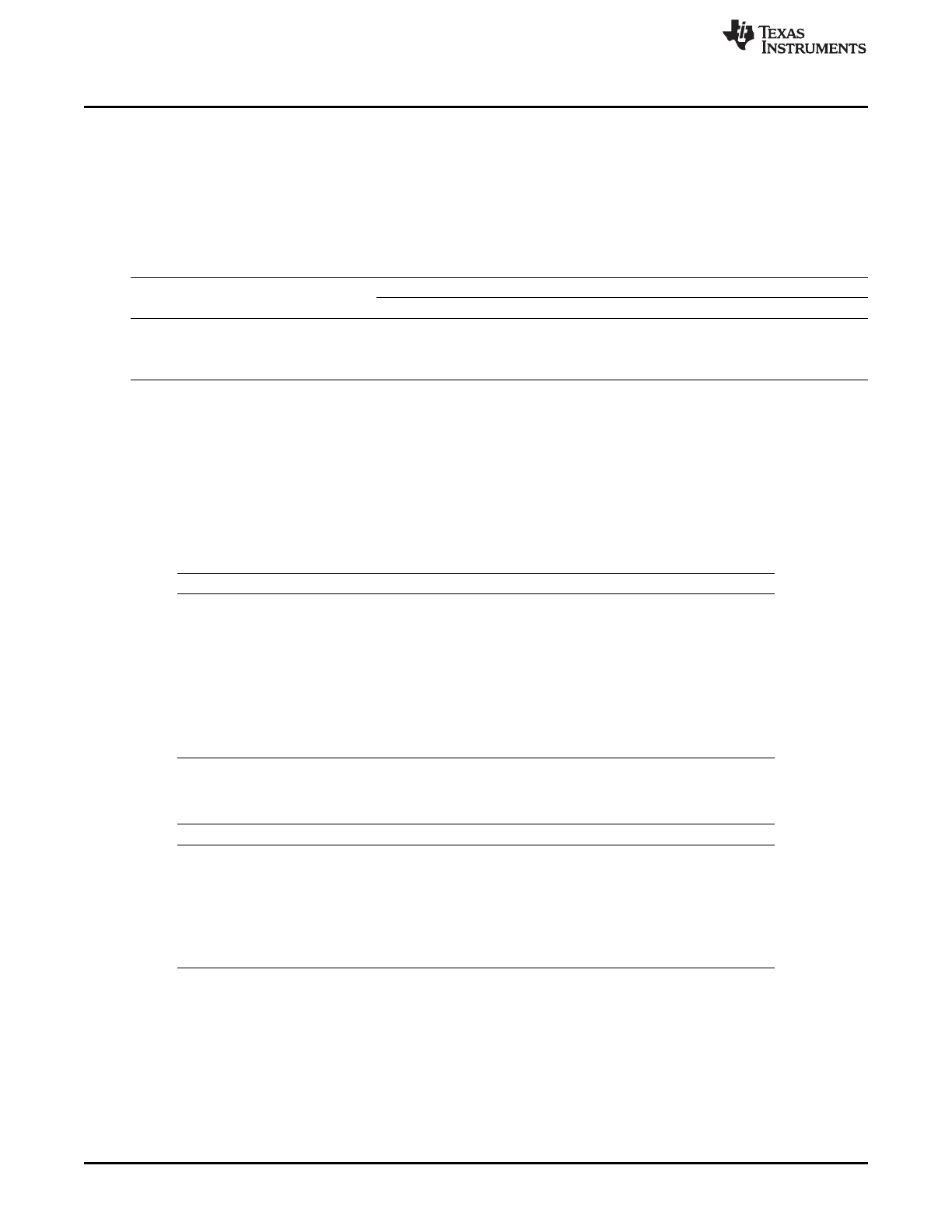

11.3.9 EDMA3 Interrupts

The EDMA3 interrupts are divided into 2 categories: transfer completion interrupts and error interrupts.

There are nine region interrupts, eight shadow regions and one global region. The transfer completion

interrupts are listed in Table 11-13. The transfer completion interrupts and the error interrupts from the

transfer controllers are all routed to the ARM interrupt controllers.

Table 11-13. EDMA3 Transfer Completion Interrupts

Name Description

EDMA3CC_INT0 EDMA3CC Transfer Completion Interrupt Shadow Region 0

EDMA3CC_INT1 EDMA3CC Transfer Completion Interrupt Shadow Region 1

EDMA3CC_INT2 EDMA3CC Transfer Completion Interrupt Shadow Region 2

EDMA3CC_INT3 EDMA3CC Transfer Completion Interrupt Shadow Region 3

EDMA3CC_INT4 EDMA3CC Transfer Completion Interrupt Shadow Region 4

EDMA3CC_INT5 EDMA3CC Transfer Completion Interrupt Shadow Region 5

EDMA3CC_INT6 EDMA3CC Transfer Completion Interrupt Shadow Region 6

EDMA3CC_INT7 EDMA3CC Transfer Completion Interrupt Shadow Region 7

Table 11-14. EDMA3 Error Interrupts

Name Description

EDMA3CC_ERRINT EDMA3CC Error Interrupt

EDMA3CC_MPINT EDMA3CC Memory Protection Interrupt

EDMA3TC0_ERRINT TC0 Error Interrupt

EDMA3TC1_ERRINT TC1 Error Interrupt

EDMA3TC2_ERRINT TC2 Error Interrupt

EDMA3TC3_ERRINT TC3 Error Interrupt

11.3.9.1 Transfer Completion Interrupts

The EDMA3CC is responsible for generating transfer completion interrupts to the CPU(s) (and other

EDMA3 masters). The EDMA3 generates a single completion interrupt per shadow region, as well as one

for the global region on behalf of all 64 channels. The various control registers and bit fields facilitate

EDMA3 interrupt generation.

The software architecture should either use the global interrupt or the shadow interrupts, but not both.

902

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...