www.ti.com

CONTROL_MODULE Registers

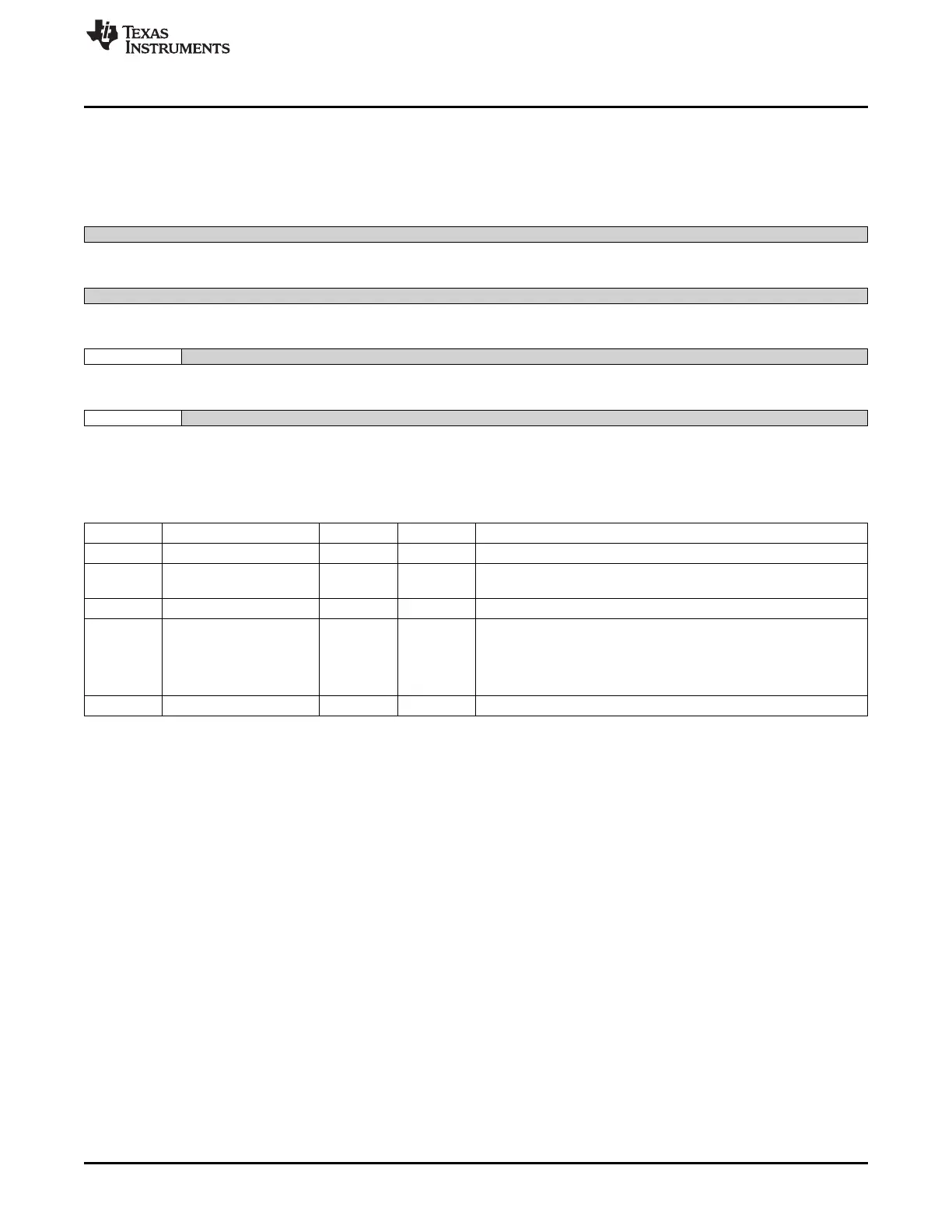

9.3.19 mmu_cfg Register (offset = 610h) [reset = 0h]

mmu_cfg is shown in Figure 9-22 and described in Table 9-29.

Figure 9-22. mmu_cfg Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

mmu_abort Reserved

R/W-0h R-0h

7 6 5 4 3 2 1 0

mmu_disable Reserved

R/W-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

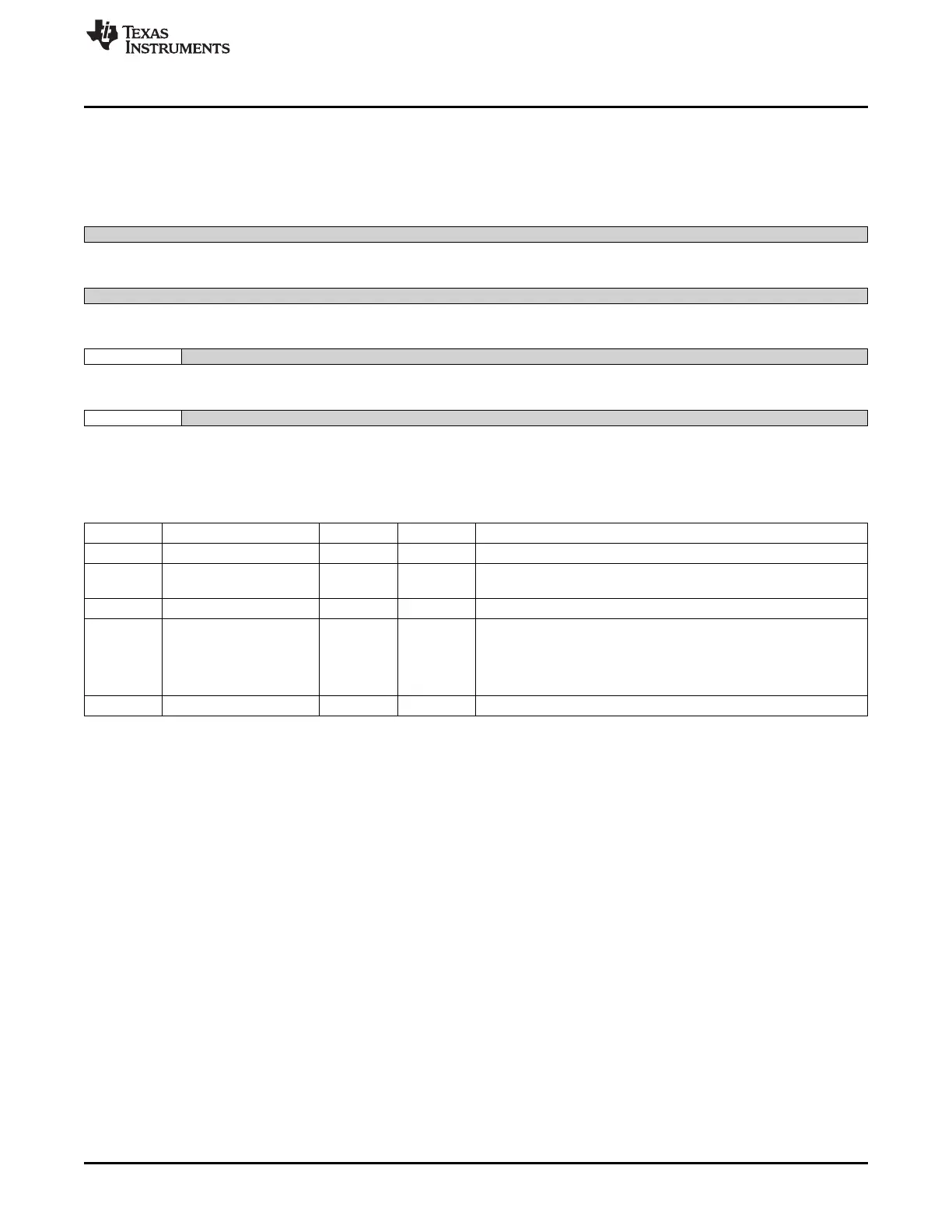

Table 9-29. mmu_cfg Register Field Descriptions

Bit Field Type Reset Description

31-16 Reserved R 0h

15 mmu_abort R/W 0h MMU abort operation This bit causes the MMU to abort the current

operation in case of lockup.

14-8 Reserved R 0h

7 mmu_disable R/W 0h MMU Disable Setting this bit disables MMU table lookup and causes

accesses to use the non-translated address.

This bit defaults to enabled but an identical bit within an MMU

configuration register defaults to disabled and must be set after the

page tables are programmed for MMU operation.

6-0 Reserved R 0h

781

SPRUH73H–October 2011–Revised April 2013 Control Module

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...