www.ti.com

UART Registers

19.5.1.14 Line Status Register (LSR) - CIR Mode

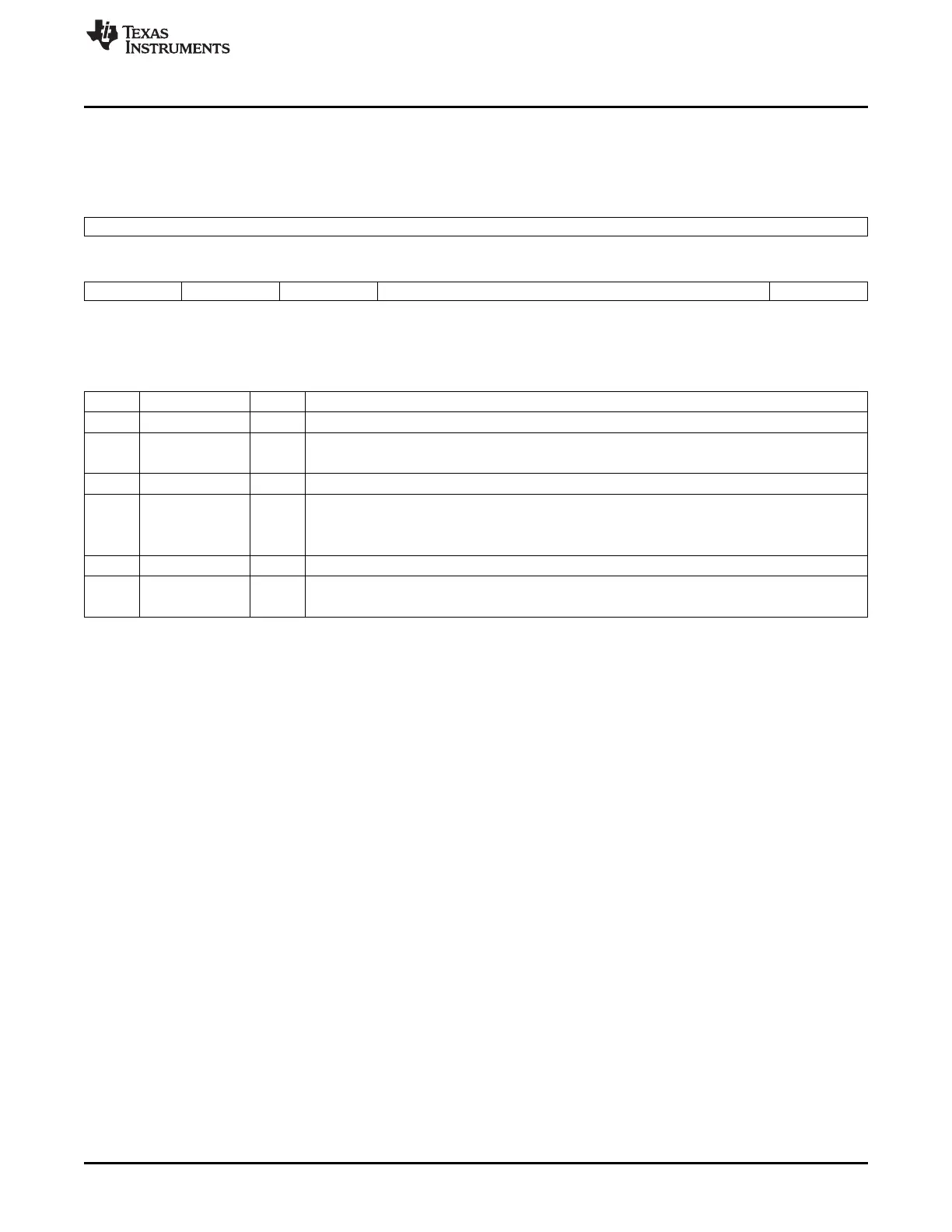

The CIR line status register (LSR) is shown in Figure 19-47 and described in Table 19-43.

Figure 19-47. CIR Line Status Register (LSR)

15 8

Reserved

R-0

7 6 5 4 1 0

THREMPTY Reserved RXSTOP Reserved RXFIFOE

R-1 R-0 R-0 R-0 R-1

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

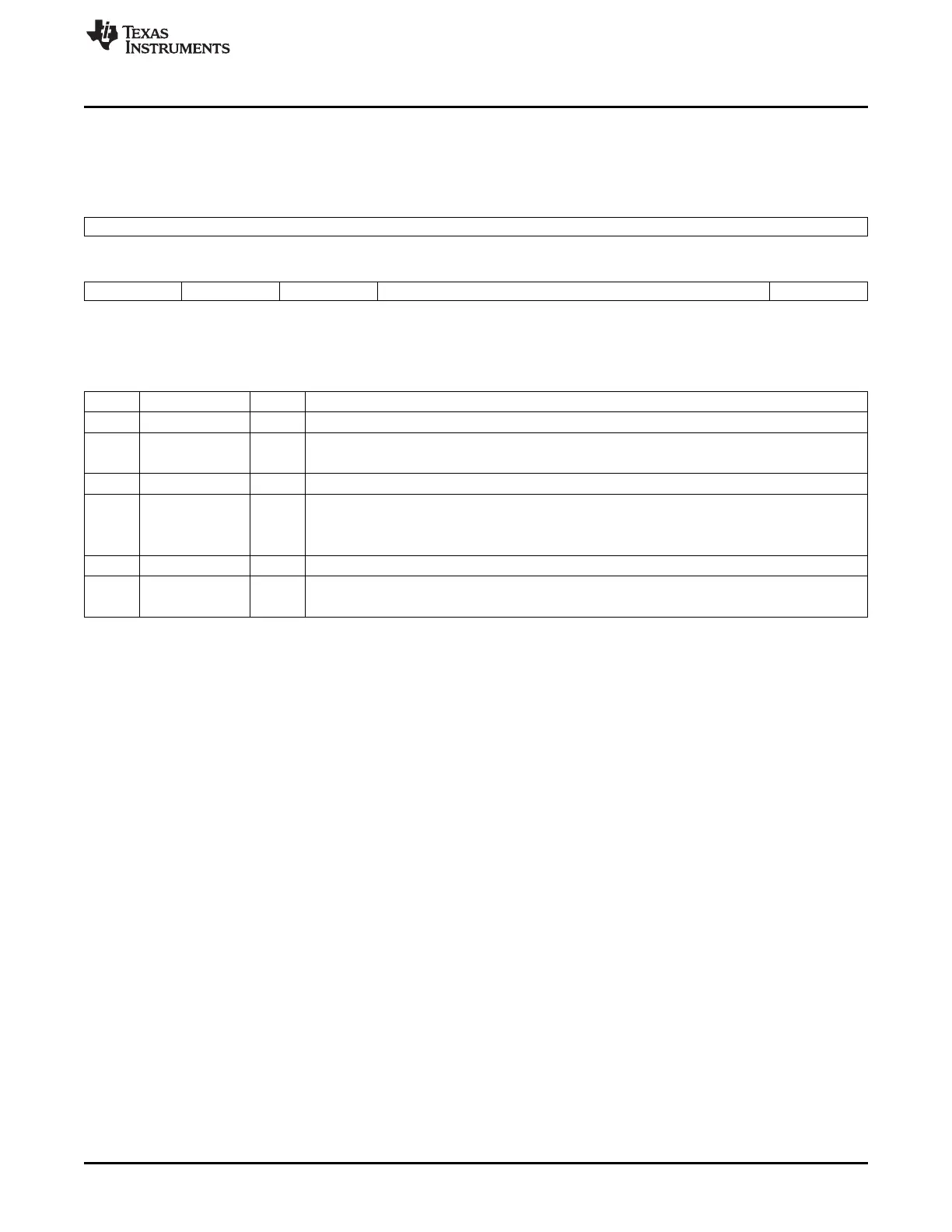

Table 19-43. CIR Line Status Register (LSR) Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7 THREMPTY 0 Transmit holding register (TX FIFO) is not empty.

1 Transmit hold register (TX FIFO) is empty. The transmission is not necessarily completed.

6 Reserved 0 Reserved.

5 RXSTOP The RXSTOP is generated based on the value set in the BOF Length register (EBLR).

0 Reception is on going or waiting for a new frame.

1 Reception is completed. It is cleared on a single read of the LSR register.

4-1 Reserved 0 Reserved

0 RXFIFOE 0 At least one data character in the RX FIFO.

1 No data in the receive FIFO.

3519

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...