www.ti.com

EMIF

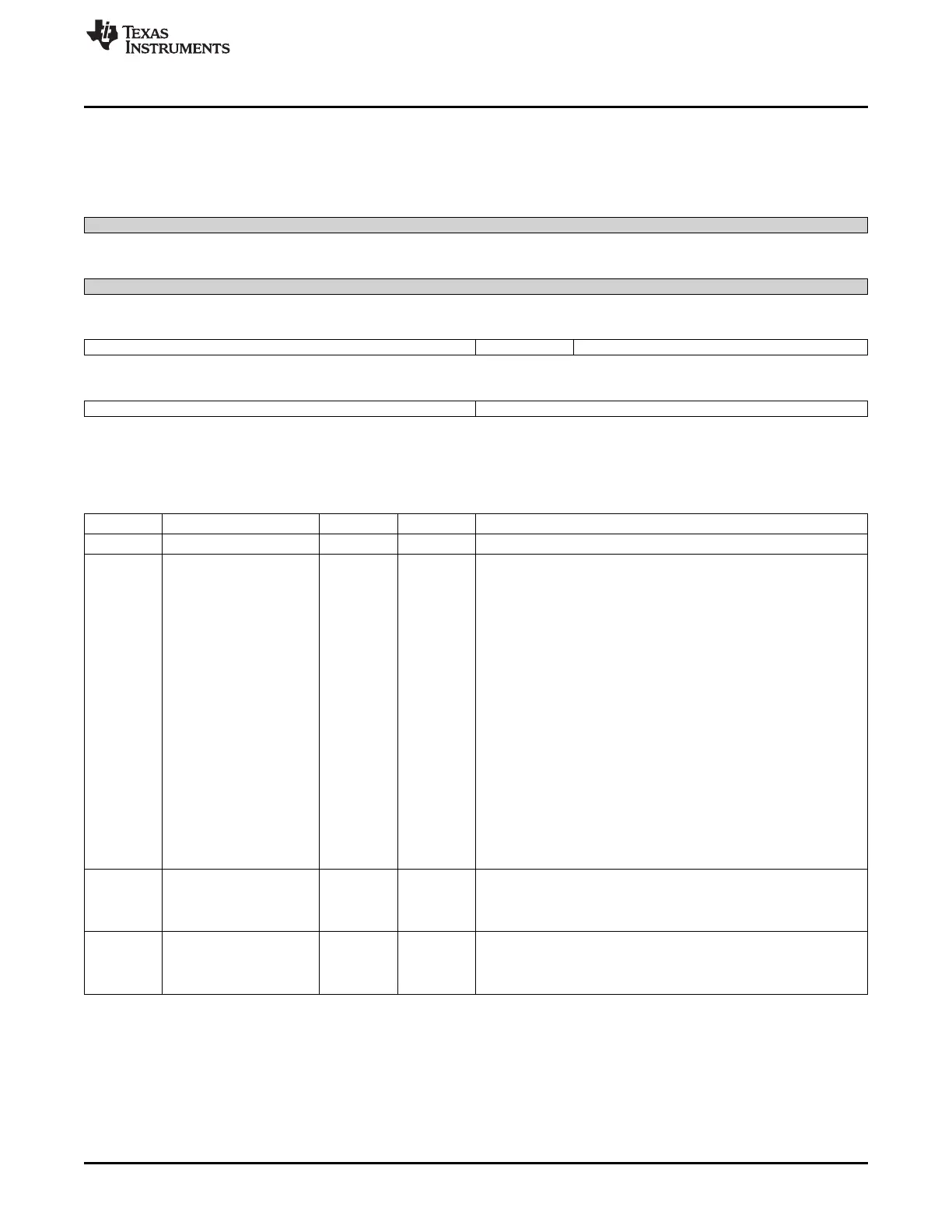

7.3.5.13 PWR_MGMT_CTRL Register (offset = 38h) [reset = 0h]

PWR_MGMT_CTRL is shown in Figure 7-103 and described in Table 7-123.

Figure 7-103. PWR_MGMT_CTRL Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

reg_pd_tim reg_dpd_en reg_lp_mode

R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

reg_sr_tim reg_cs_tim

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

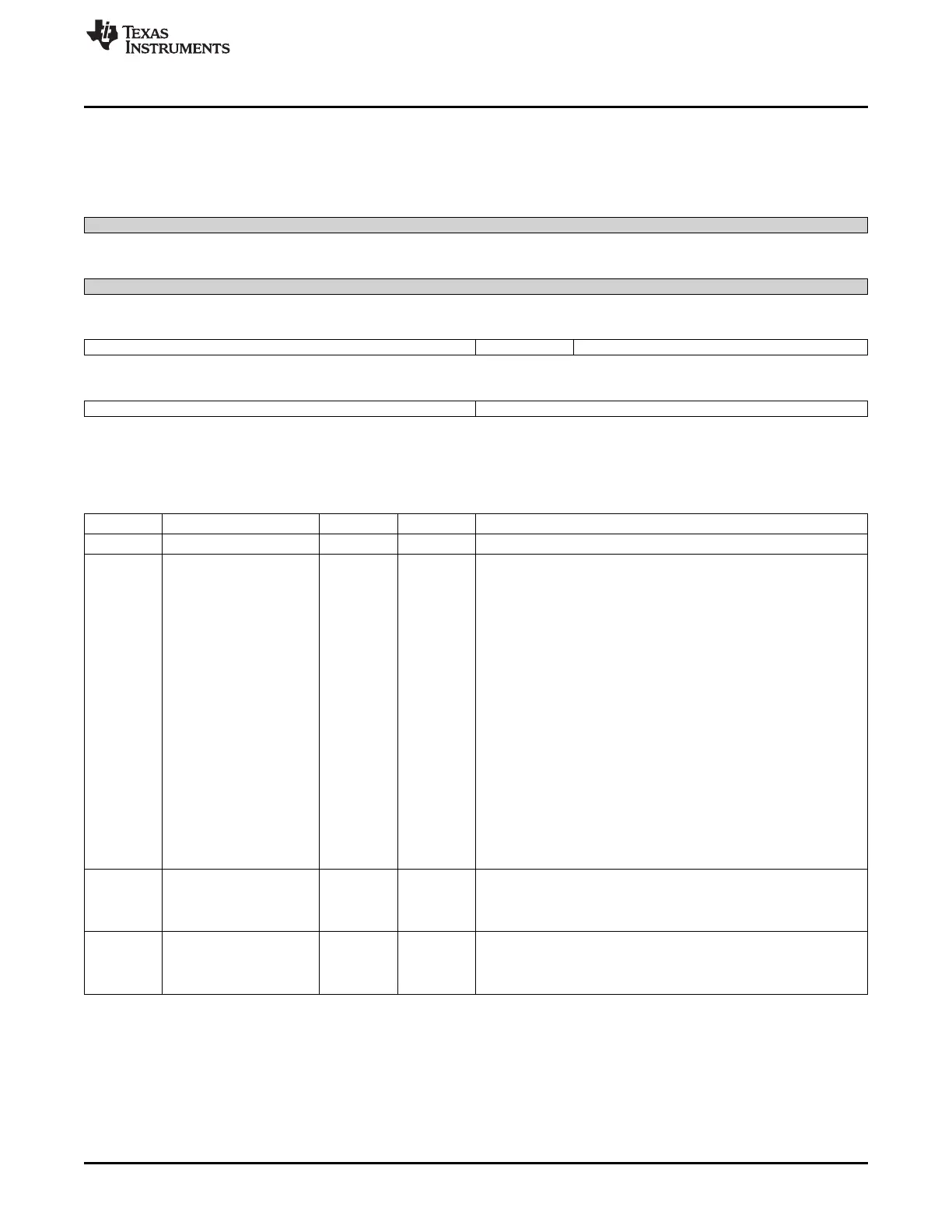

Table 7-123. PWR_MGMT_CTRL Register Field Descriptions

Bit Field Type Reset Description

31-16 Reserved R 0h

15-12 reg_pd_tim R/W 0h Power Mangement timer for Power-Down.

The EMIF will put the external SDRAM in Power-Down mode after

the EMIF is idle for these number of DDR clock cycles and if

reg_lp_mode field is set to 4.

Set to 0 to immediately enter Power-Down mode.

Set to 1 for 16 clocks.

Set to 2 for 32 clocks.

Set to 3 for 64 clocks.

Set to 4 for 128 clocks.

Set to 5 for 256 clocks.

Set to 6 for 512 clocks.

Set to 7 for 1024 clocks.

Set to 8 for 2048 clocks.

Set to 9 for 4096 clocks.

Set to 10 for 8192 clocks.

Set to 11 for 16384 clocks.

Set to 12 for 32768 clocks.

Set to 13 for 65536 clocks.

Set to 14 for 131072 clocks.

Set to 15 for 262144 clocks.

Note: After updating this field, at least one dummy read access to

SDRAM is required for the new value to take affect.

11 reg_dpd_en R/W 0h Deep Power Down enable.

Set to 0 for normal operation.

Set to 1 to enter deep power down mode.

This mode will override the reg_lp_mode field setting.

10-8 reg_lp_mode R/W 0h Automatic Power Management enable.

Set to 1 for Clock Stop, set to 2 for Self Refresh, and set to 4 for

Power-Down.

All other values will disable automatic power management.

437

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...