www.ti.com

USB Registers

16.5.1.42 IRQFRAMEENABLE1 Register (offset = 244h) [reset = 0h]

IRQFRAMEENABLE1 is shown in Figure 16-63 and described in Table 16-71.

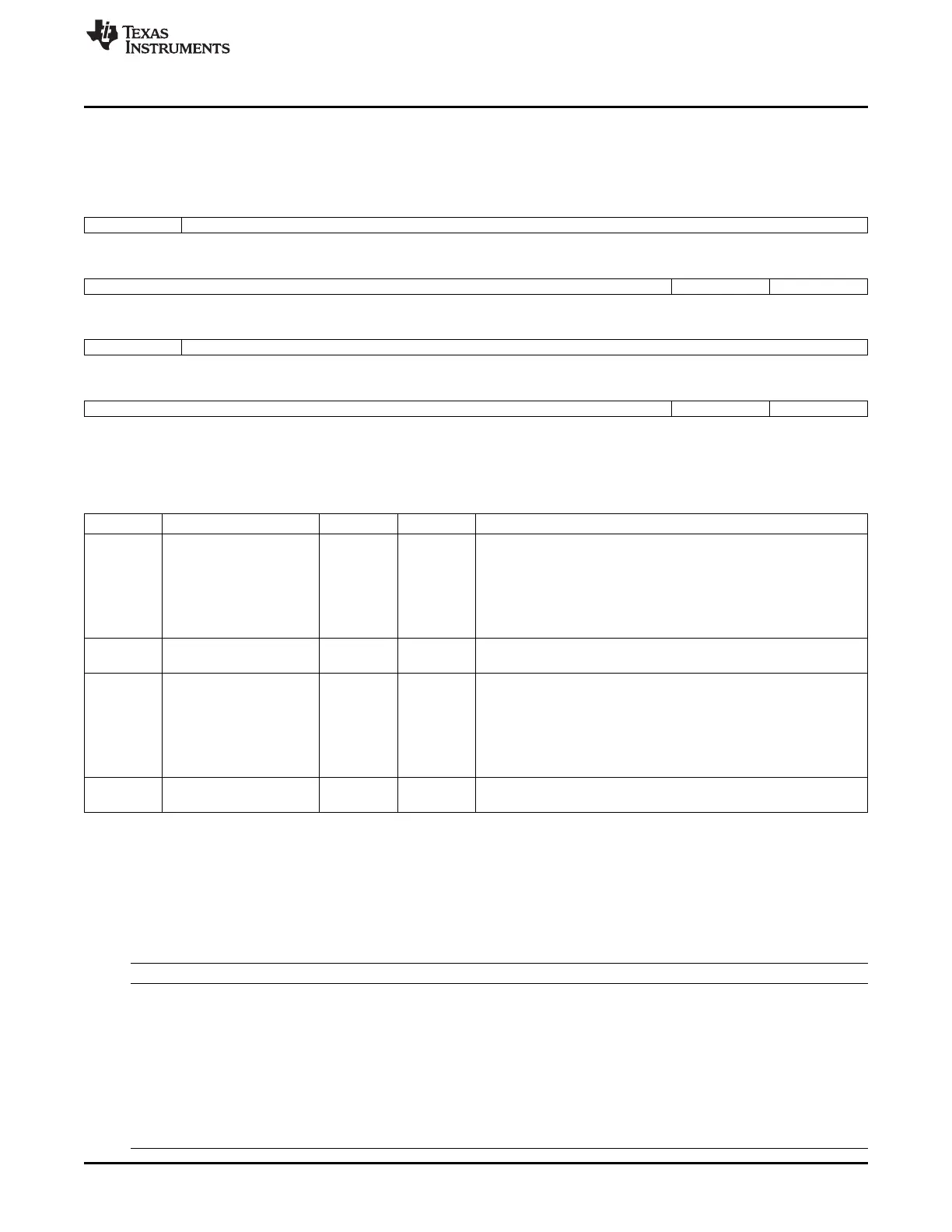

Figure 16-63. IRQFRAMEENABLE1 Register

31 30 29 28 27 26 25 24

FRAME_EN_RX1_15 Reserved

R/W-0h

23 22 21 20 19 18 17 16

Reserved FRAME_EN_RX1_1 Reserved

R/W-0h

15 14 13 12 11 10 9 8

FRAME_EN_TX1_15 Reserved

R/W-0h

7 6 5 4 3 2 1 0

Reserved FRAME_EN_TX1_1 Reserved

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

Table 16-71. IRQFRAMEENABLE1 Register Field Descriptions

Bit Field Type Reset Description

31 FRAME_EN_RX1_15 R/W 0h FRAME threshold enable value for rx_pkt_cmp_1 for USB1 Endpoint

15.

...

...

...

...

...

17 FRAME_EN_RX1_1 R/W 0h FRAME threshold enable value for rx_pkt_cmp_1 for USB1 Endpoint

1.

15 FRAME_EN_TX1_15 R/W 0h FRAME threshold enable value for tx_pkt_cmp_1 for USB1 Endpoint

15.

...

...

...

...

...

1 FRAME_EN_TX1_1 R/W 0h FRAME threshold enable value for tx_pkt_cmp_1 for USB1 Endpoint

1.

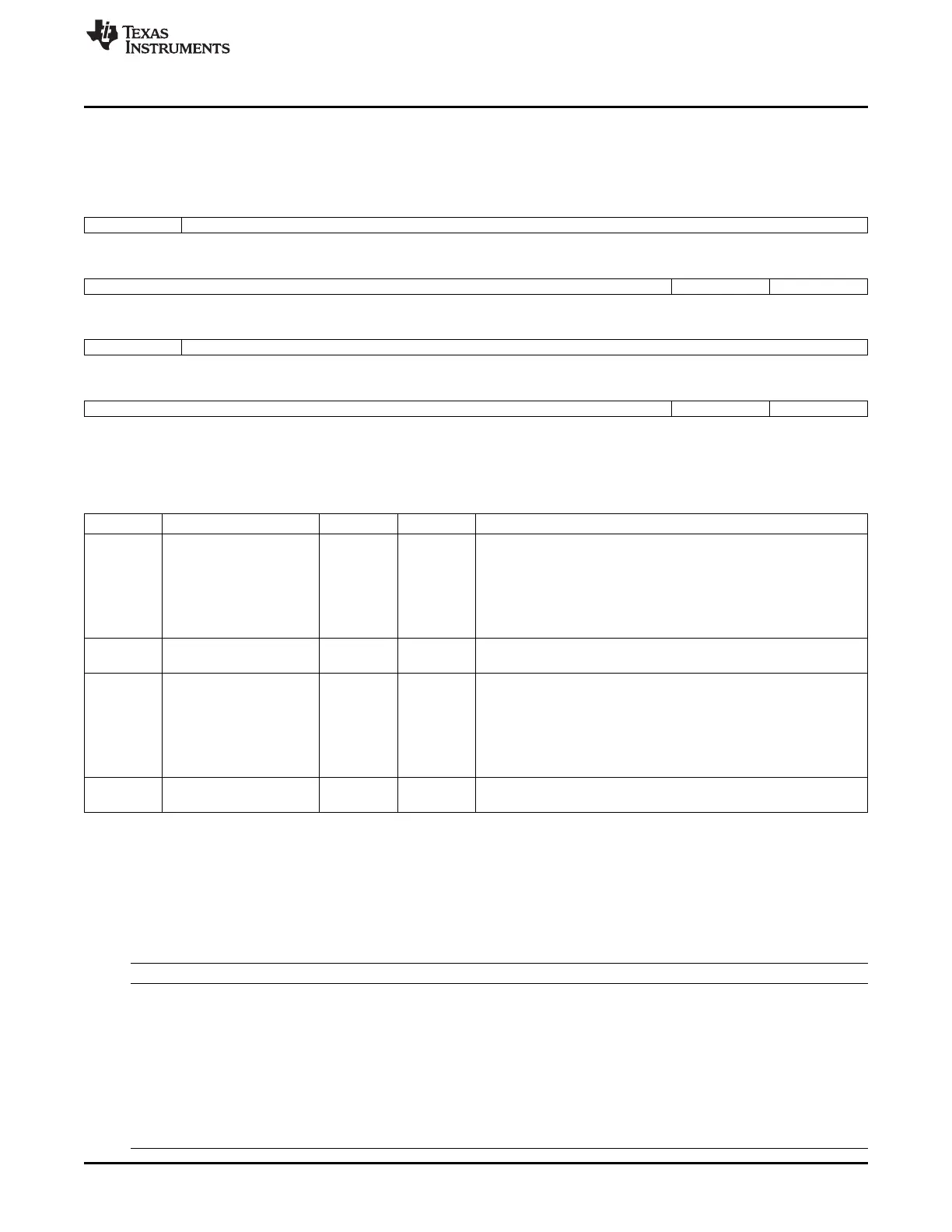

16.5.2 USB0_CTRL Registers

Table 16-72 lists the memory-mapped registers for the USB0_CTRL. All register offset addresses not

listed in Table 16-72 should be considered as reserved locations and the register contents should not be

modified.

Table 16-72. USB0_CTRL REGISTERS

Offset Acronym Register Name Section

0h USB0REV Section 16.5.2.1

14h USB0CTRL Section 16.5.2.2

18h USB0STAT Section 16.5.2.3

20h USB0IRQMSTAT Section 16.5.2.4

28h USB0IRQSTATRAW0 Section 16.5.2.5

2Ch USB0IRQSTATRAW1 Section 16.5.2.6

30h USB0IRQSTAT0 Section 16.5.2.7

34h USB0IRQSTAT1 Section 16.5.2.8

1803

SPRUH73H–October 2011–Revised April 2013 Universal Serial Bus (USB)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...