Ethernet Subsystem Registers

www.ti.com

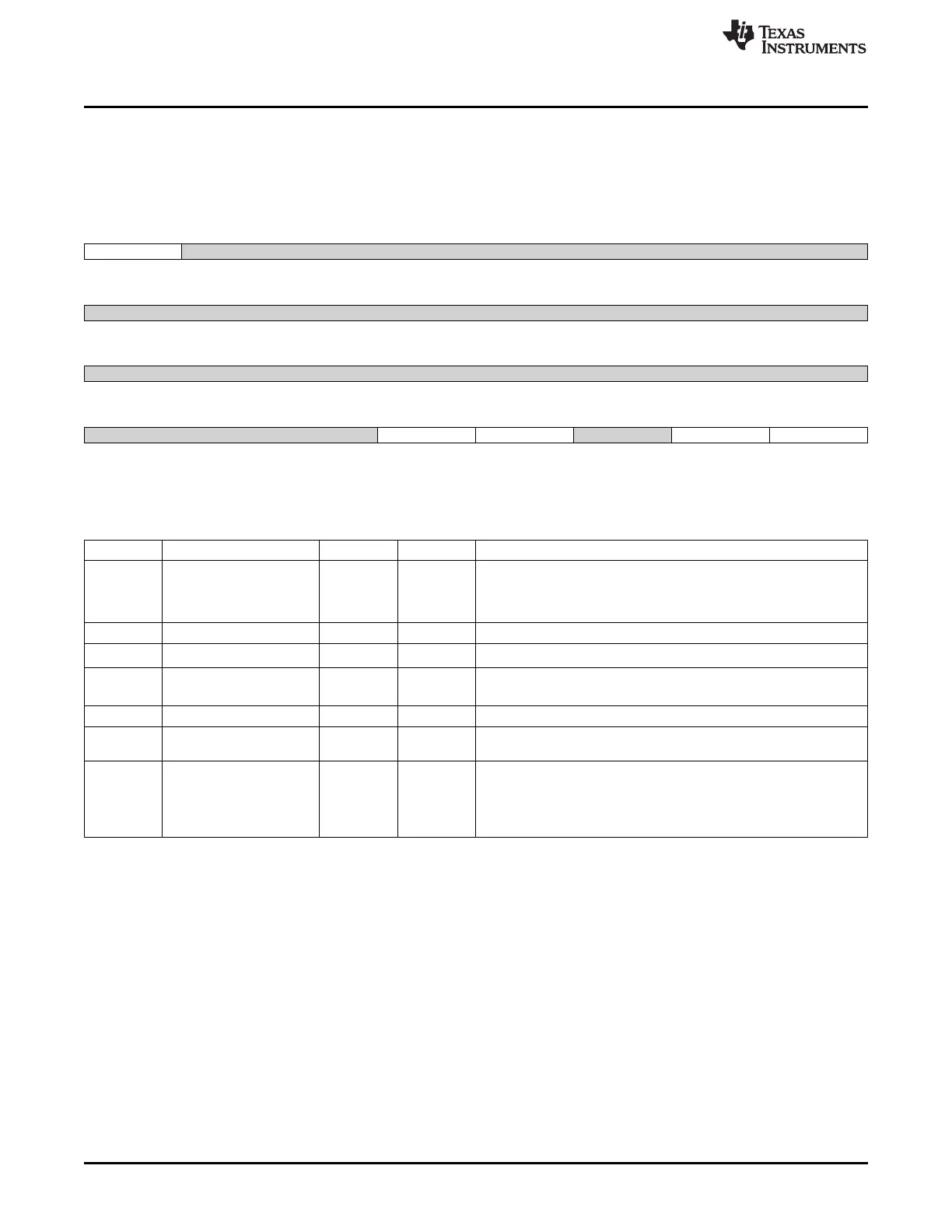

14.5.7.3 MACSTATUS Register (offset = 8h) [reset = 0h]

MACSTATUS is shown in Figure 14-175 and described in Table 14-191.

CPGMAC_SL MAC STATUS REGISTER

Figure 14-175. MACSTATUS Register

31 30 29 28 27 26 25 24

IDLE Reserved

R-0h R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved EXT_GIG EXT_FULLDUPLEX Reserved RX_FLOW_ACT TX_FLOW_ACT

R-0h R-0h R-0h R-0h R-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

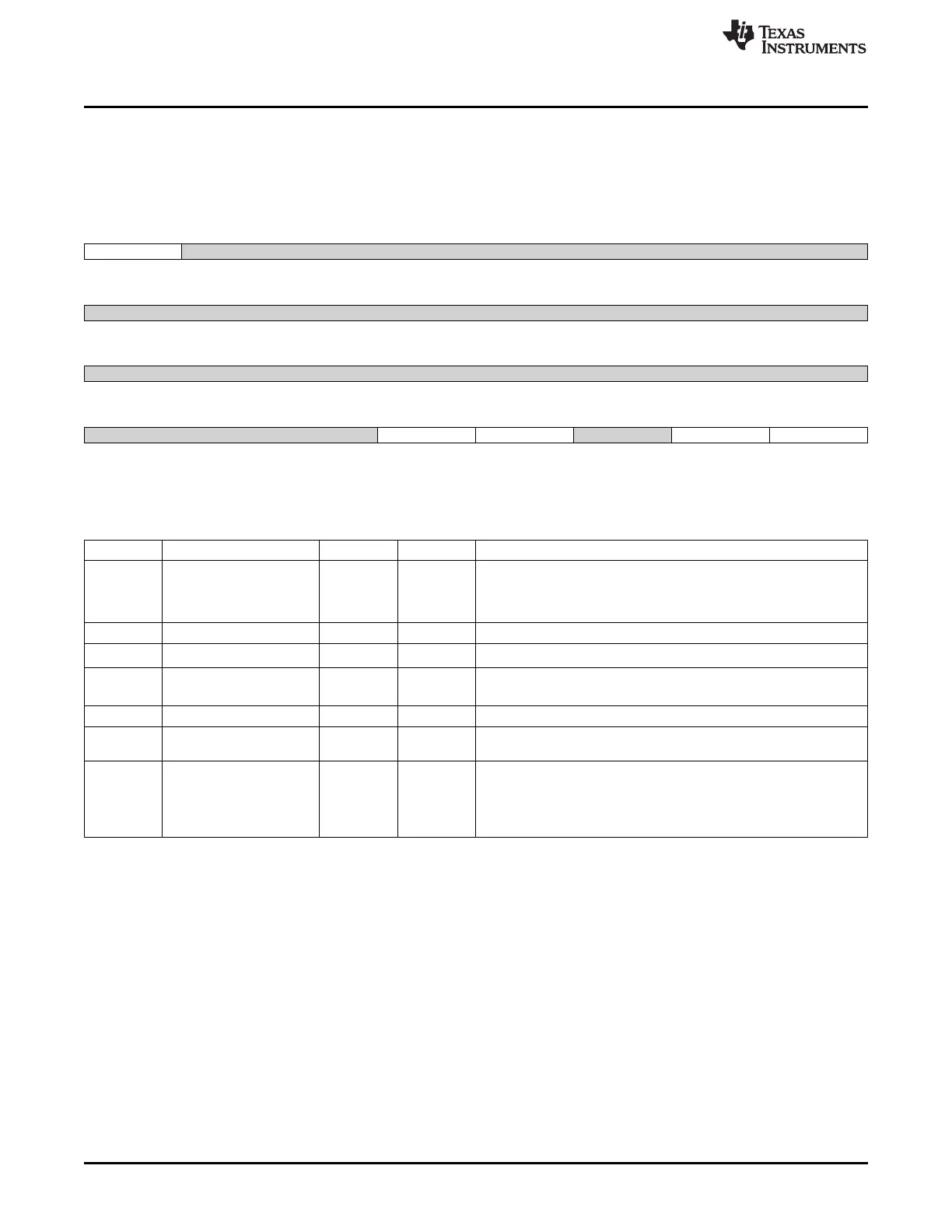

Table 14-191. MACSTATUS Register Field Descriptions

Bit Field Type Reset Description

31 IDLE R 0h CPGMAC_SL IDLE - The CPGMAC_SL is in the idle state (valid

after an idle command)

0 - The CPGMAC_SL is not in the idle state.

1 - The CPGMAC_SL is in the idle state.

30-5 Reserved R 0h

4 EXT_GIG R 0h

External GIG - This is the value of the EXT_GIG input bit.

3 EXT_FULLDUPLEX R 0h

External Fullduplex - This is the value of the EXT_FULLDUPLEX

input bit.

2 Reserved R 0h

1 RX_FLOW_ACT R 0h Receive Flow Control Active - When asserted, indicates that receive

flow control is enabled and triggered.

0 TX_FLOW_ACT R 0h Transmit Flow Control Active - When asserted, this bit indicates that

the pause time period is being observed for a received pause frame.

No new transmissions will begin while this bit is asserted except for

the transmission of pause frames.

Any transmission in progress when this bit is asserted will complete.

1416

Ethernet Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...