McSPI Registers

www.ti.com

24.4.1.6 McSPI System Register (MCSPI_SYST)

This McSPI system register (MCSPI_SYST) is used to configure the system interconnect either internally

to the peripheral bus or externally to the device I/O pads, when the module is configured in the system

test (SYSTEST) mode. The MCSPI_SYST is shown in Figure 24-31 and described in Table 24-16.

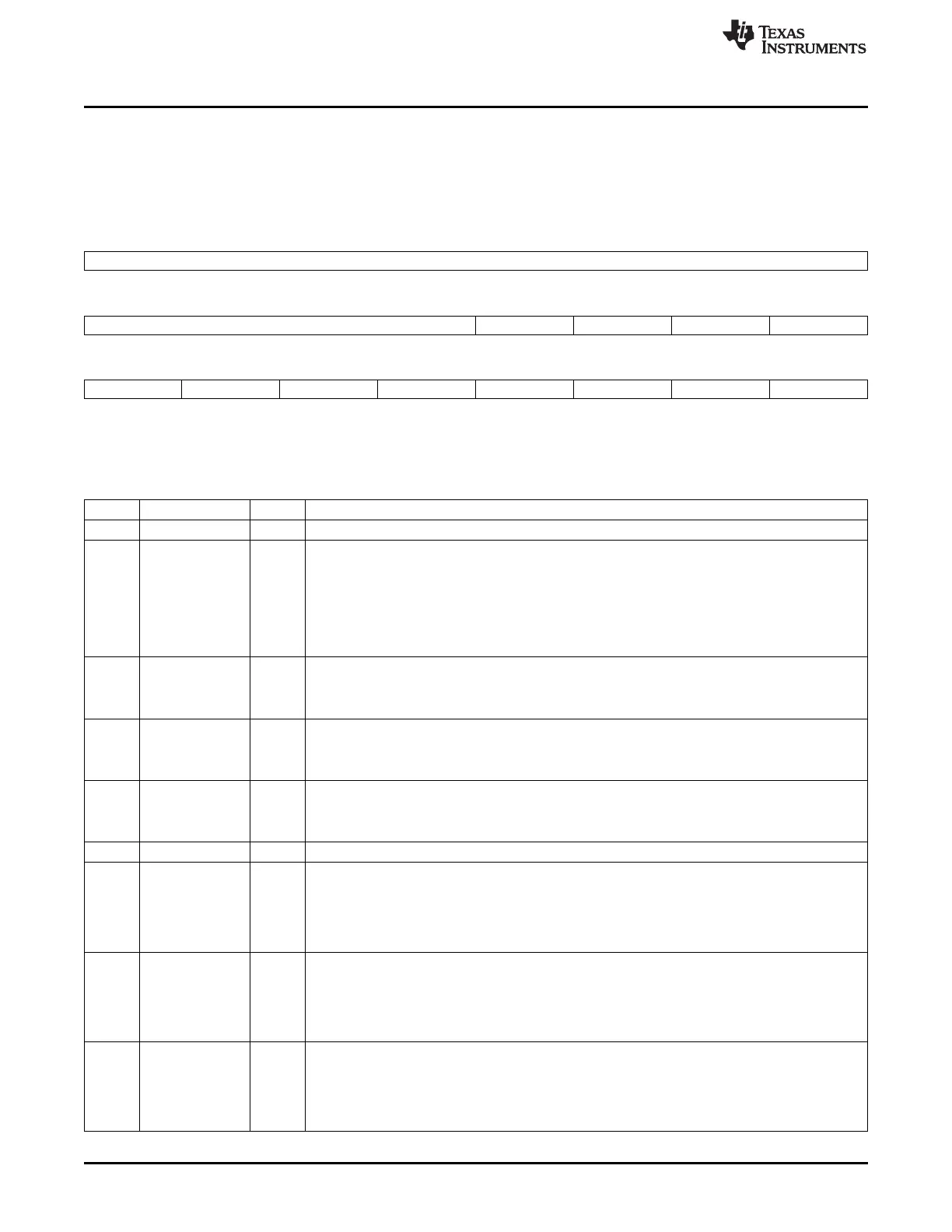

Figure 24-31. McSPI System Register (MCSPI_SYST)

31 16

Reserved

R/W-0

15 12 11 10 9 8

Reserved SSB SPIENDIR SPIDATDIR1 SPIDATDIR0

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

Reserved SPICLK SPIDAT_1 SPIDAT_0 SPIEN_3 SPIEN_2 SPIEN_1 SPIEN_0

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; -n = value after reset

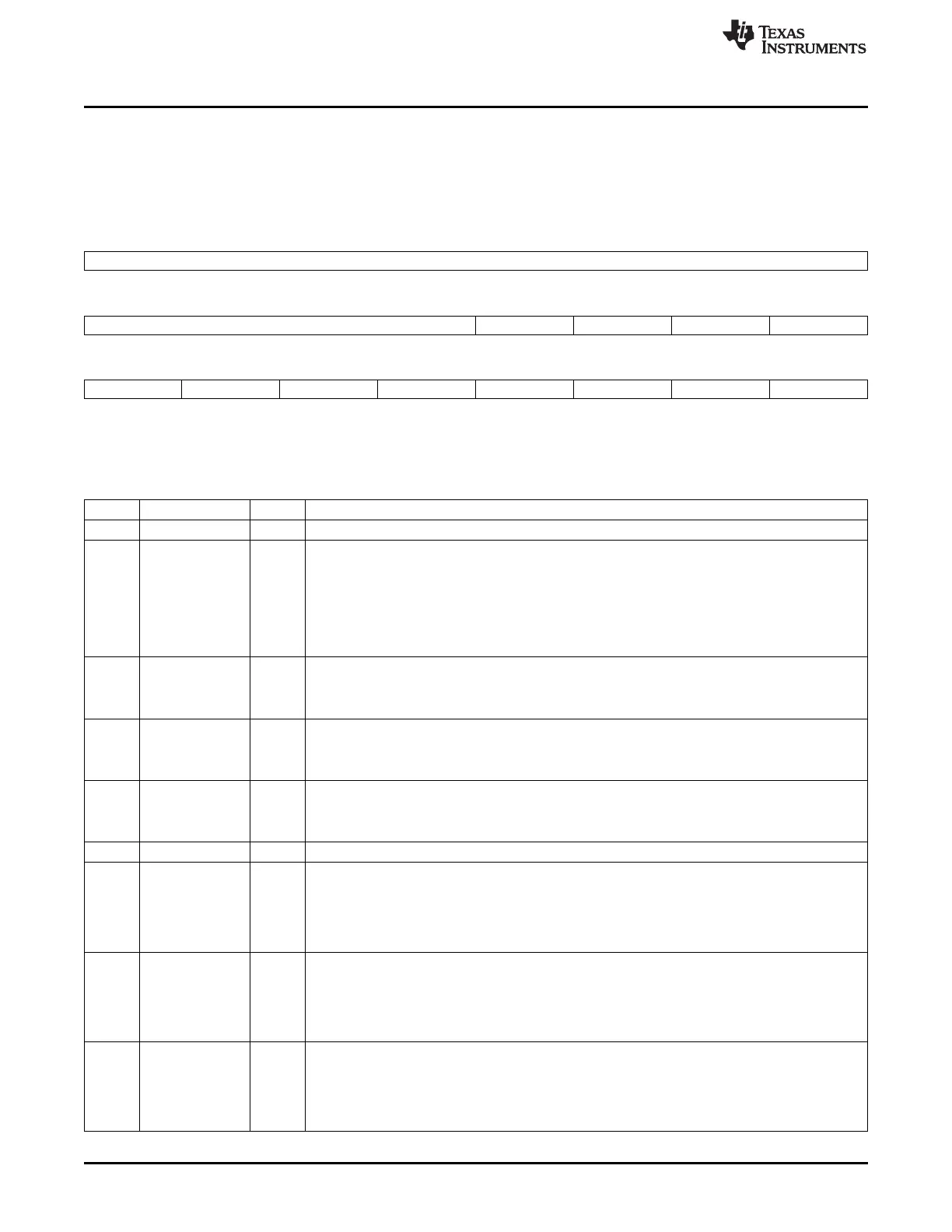

Table 24-16. McSPI System Register (MCSPI_SYST) Field Descriptions

Bit Field Value Description

31-12 Reserved 0 Reads returns 0

11 SSB Set status bit. This bit must be cleared prior attempting to clear a status bit of the MCSPI_

IRQSTATUS register.

0 No action. Writing 0 does not clear already set status bits.

This bit must be cleared prior attempting to clear a status bit of the <MCSPI_IRQSTATUS> register.

1 Writing 1 sets to 1 all status bits contained in the MCSPI_IRQSTATUS register.

Writing 1 into this bit sets to 1 all status bits contained in the <MCSPI_IRQSTATUS> register.

10 SPIENDIR Sets the direction of the SPIEN[3:0] lines and SPICLK line.

0 Output (as in master mode).

1 Input (as in slave mode).

9 SPIDATDIR1 Sets the direction of the SPIDAT[1].

0 Output

1 Input

8 SPIDATDIR0 Sets the direction of the SPIDAT[0].

0 Output

1 Input

7 Reserved 0 Reserved

6 SPICLK SPICLK line (signal data value)

If MCSPI_SYST[SPIENDIR] = 1 (input mode direction), this bit returns the value on the CLKSPI line

(high or low), and a write into this bit has no effect.

If MCSPI_SYST[SPIENDIR] = 0 (output mode direction), the CLKSPI line is driven high or low

according to the value written into this register.

5 SPIDAT_1 SPIDAT[1] line (signal data value)

If MCSPI_SYST[SPIDATDIR1] = 0 (output mode direction), the SPIDAT[1] line is driven high or low

according to the value written into this register.

If MCSPI_SYST[SPIDATDIR1] = 1 (input mode direction), this bit returns the value on the

SPIDAT[1] line (high or low), and a write into this bit has no effect.

4 SPIDAT_0 SPIDAT[0] line (signal data value)

If MCSPI_SYST[SPIDATDIR0] = 0 (output mode direction), the SPIDAT[0] line is driven high or low

according to the value written into this register.

If MCSPI_SYST[SPIDATDIR0] = 1 (input mode direction), this bit returns the value on the

SPIDAT[0] line (high or low), and a write into this bit has no effect.

4042

Multichannel Serial Port Interface (McSPI) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...