I2C Registers

www.ti.com

21.4.1.24 I2C_SCLH Register (offset = B8h) [reset = 0h]

I2C_SCLH is shown in Figure 21-39 and described in Table 21-32.

CAUTION: During an active mode (I2C_EN bit in I2C_CON register is set to 1), no modification must be

done in this register. Changing it may result in an unpredictable behavior. This register is used to

determine the SCL high time value when master.

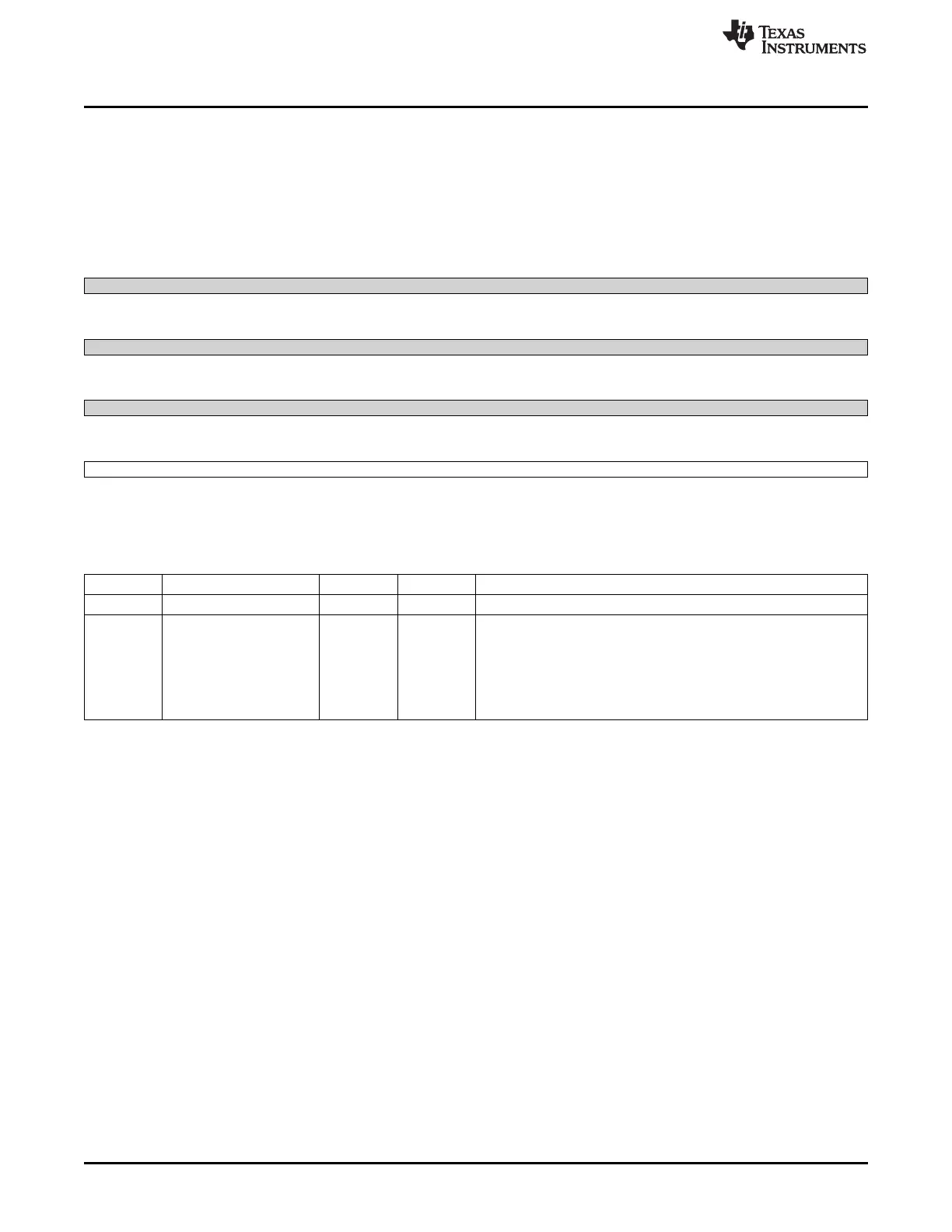

Figure 21-39. I2C_SCLH Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

SCLH

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

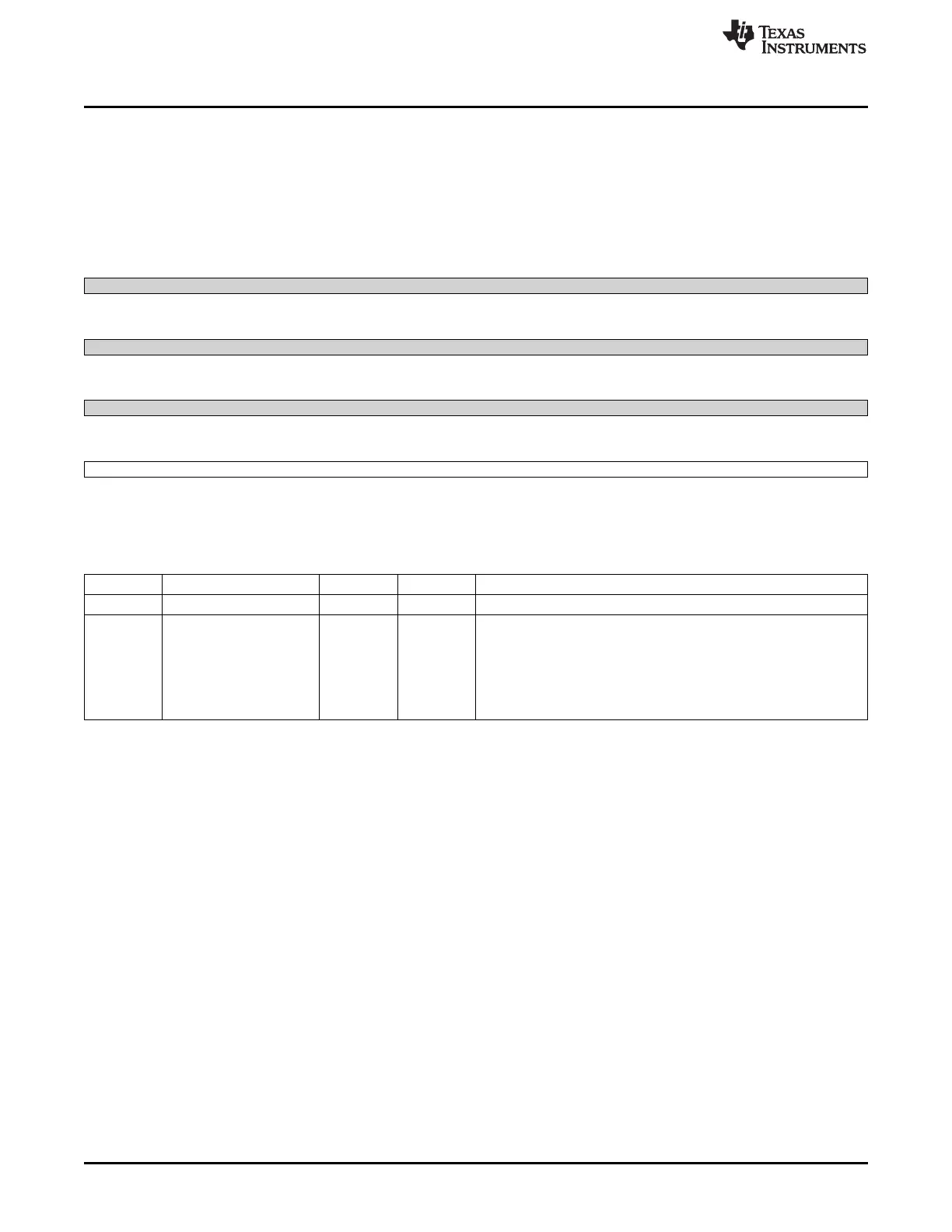

Table 21-32. I2C_SCLH Register Field Descriptions

Bit Field Type Reset Description

31-8 Reserved R 0h

7-0 SCLH R/W 0h Fast/Standard mode SCL low time.

I2C master mode only, (FS).

This

8-bit value is used to generate the SCL high time value (tHIGH)

when the peripheral is operated in master mode.

- tHIGH = (SCLH + 5) * ICLK time period.

Value after reset is low (all 8 bits).

3756

I2C SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...