USB Registers

www.ti.com

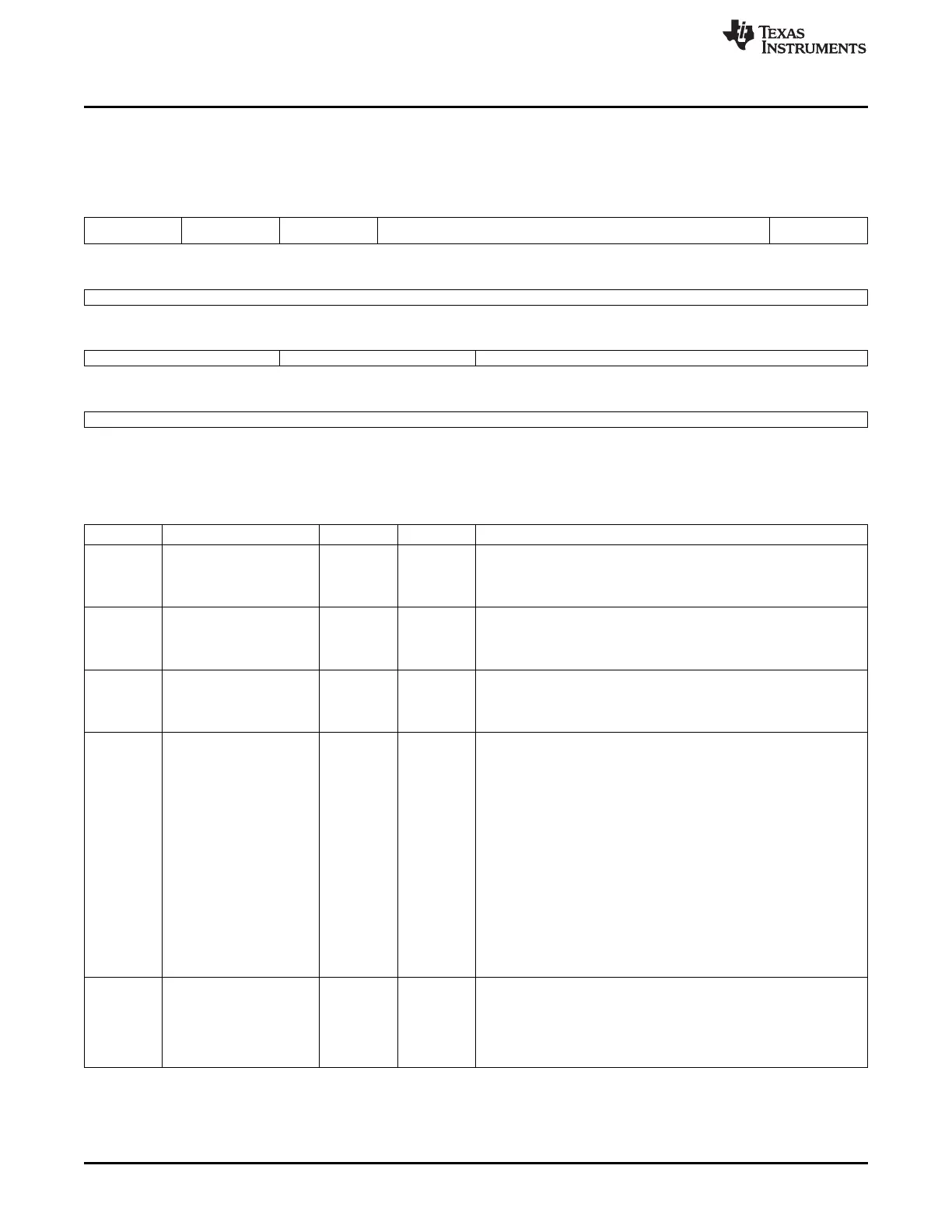

16.5.5.9 RXGCR1 Register (offset = 828h) [reset = 0h]

RXGCR1 is shown in Figure 16-160 and described in Table 16-172.

Figure 16-160. RXGCR1 Register

31 30 29 28 27 26 25 24

RX_ENABLE RX_TEARDOWN RX_PAUSE Reserved RX_ERROR_HANDLI

NG

R/W-0h R/W-0h R/W-0h W-0h

23 22 21 20 19 18 17 16

RX_SOP_OFFSET

W-0h

15 14 13 12 11 10 9 8

RX_DEFAULT_DESC_TYPE RX_DEFAULT_RQ_QMGR RX_DEFAULT_RQ_QNUM

W-0h W-0h W-0h

7 6 5 4 3 2 1 0

RX_DEFAULT_RQ_QNUM

W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

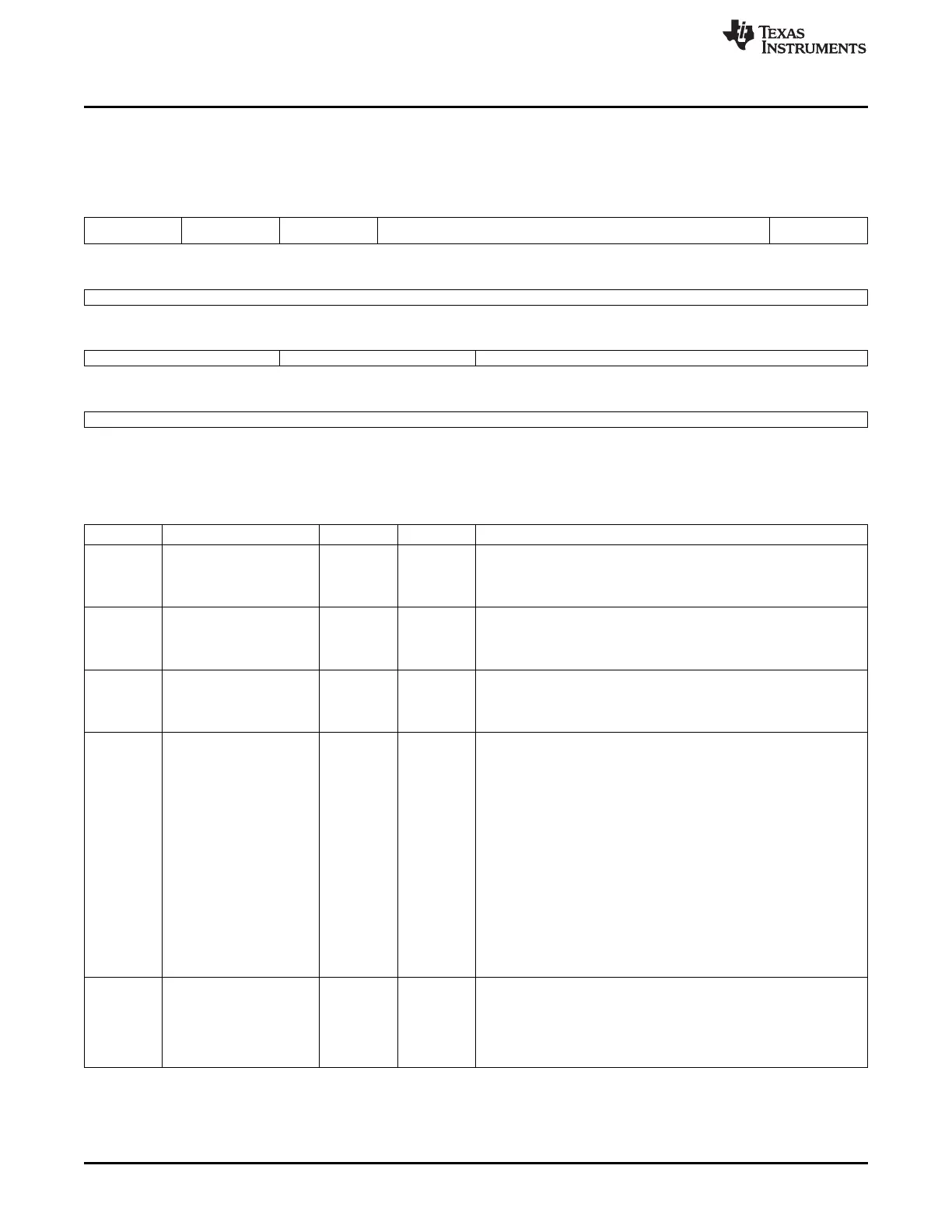

Table 16-172. RXGCR1 Register Field Descriptions

Bit Field Type Reset Description

31 RX_ENABLE R/W 0h This field enables or disables the channel

0 = channel is disabled

1 = channel is enabled This field will be cleared after a channel

teardown is complete.

30 RX_TEARDOWN R/W 0h This field indicates whether or not an Rx teardown operation is

complete.

This field should be cleared when a channel is initialized.

This field will be set after a channel teardown is complete.

29 RX_PAUSE R/W 0h Setting this bit causes the CPPI DMA to be suspended for rx

channels.

If a pause is being requested and the channel is not in a packet then

drop the credit.

24 RX_ERROR_HANDLING W 0h This bit controls the error handling mode for the channel and is only

used when channel errors (i.e.

descriptor or buffer starvation occurs):

0 = Starvation errors result in dropping packet and reclaiming any

used descriptor or buffer resources back to the original queues/pools

they were allocated to

1 = Starvation errors result in subsequent re-try of the descriptor

allocation operation.

In this mode, the DMA will return to the IDLE state without saving it's

internal operational state back to the internal state RAM and without

issuing an advance operation on the FIFO interface.

This results in the DMA re-initiating the FIFO block transfer at a later

time with the intention that additional free buffers and/or descriptors

will have been added.

Regardless of the value of this bit, the DMA will assert the

cdma_rx_sof_overrun (for SOP) or cdma_rx_mof_overrun (for non-

SOP) when

23-16 RX_SOP_OFFSET W 0h This field specifies the number of bytes that are to be skipped in the

SOP buffer before beginning to write the payload.

This value must be less than the minimum size of a buffer in the

system.

Valid values are

0 - 255 bytes.

1938

Universal Serial Bus (USB) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...