www.ti.com

Ethernet Subsystem Registers

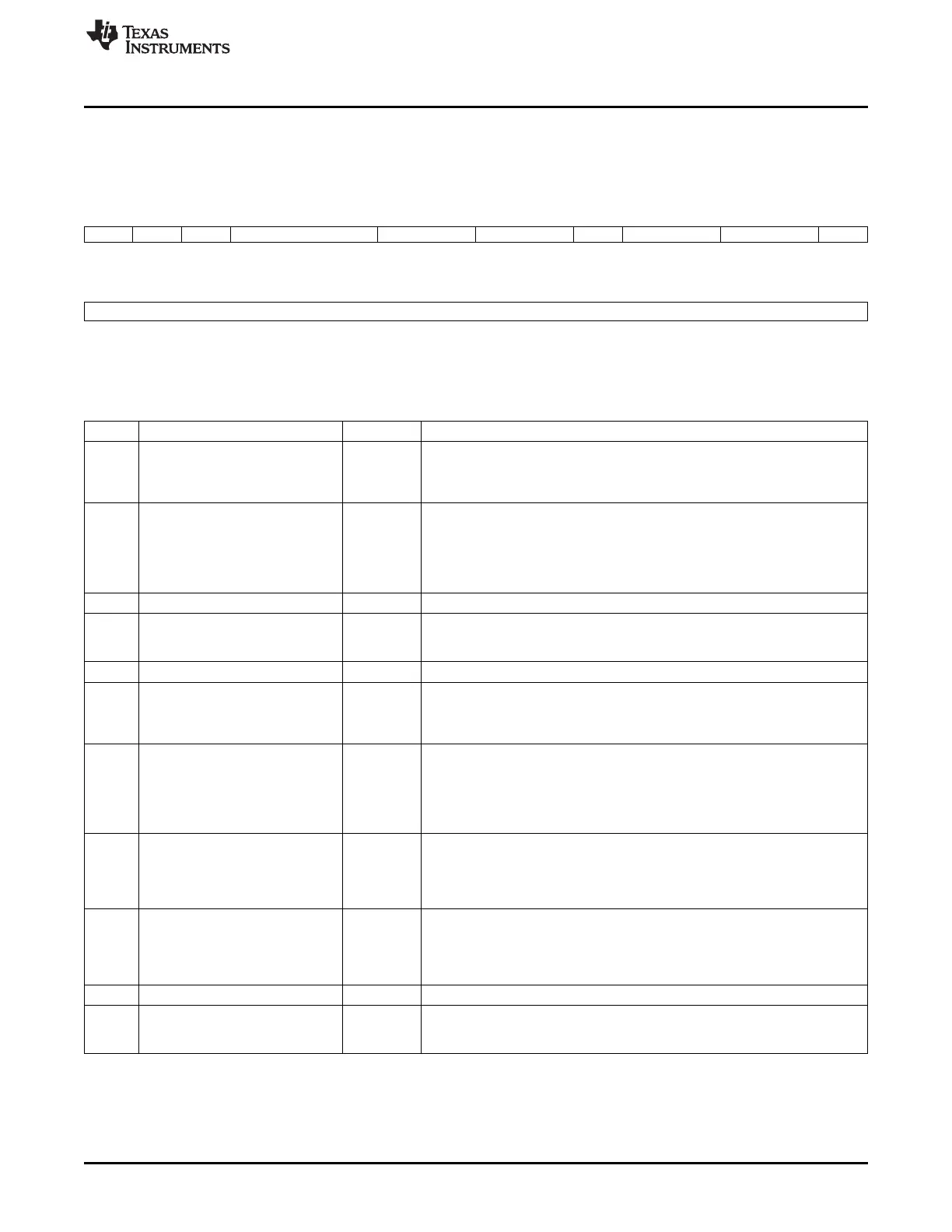

14.5.10.2 MDIO Control Register (MDIOCONTROL)

The MDIO control register (MDIOCONTROL) is shown in Figure 14-233 and described in Table 14-252.

Figure 14-233. MDIO Control Register (MDIOCONTROL)

31 30 29 28 24 23 21 20 19 18 17 16

IDLE ENABLE Reserved HIGHEST_USER_CHANNEL Reserved PREAMBLE FAULT FAULTENB INTTESTENB Reserved

R-0x1 R/W-0x0 R-0x0 R-0x1 R-0x0 R/W-0x0 RWC- R/W-0x0 R/W-0x0 R-0x0

0x0

15 0

CLKDIV

R/W-0x255

LEGEND: R/W = Read/Write; RWC = Read/Write/Clear; R = Read only; -n = value after reset

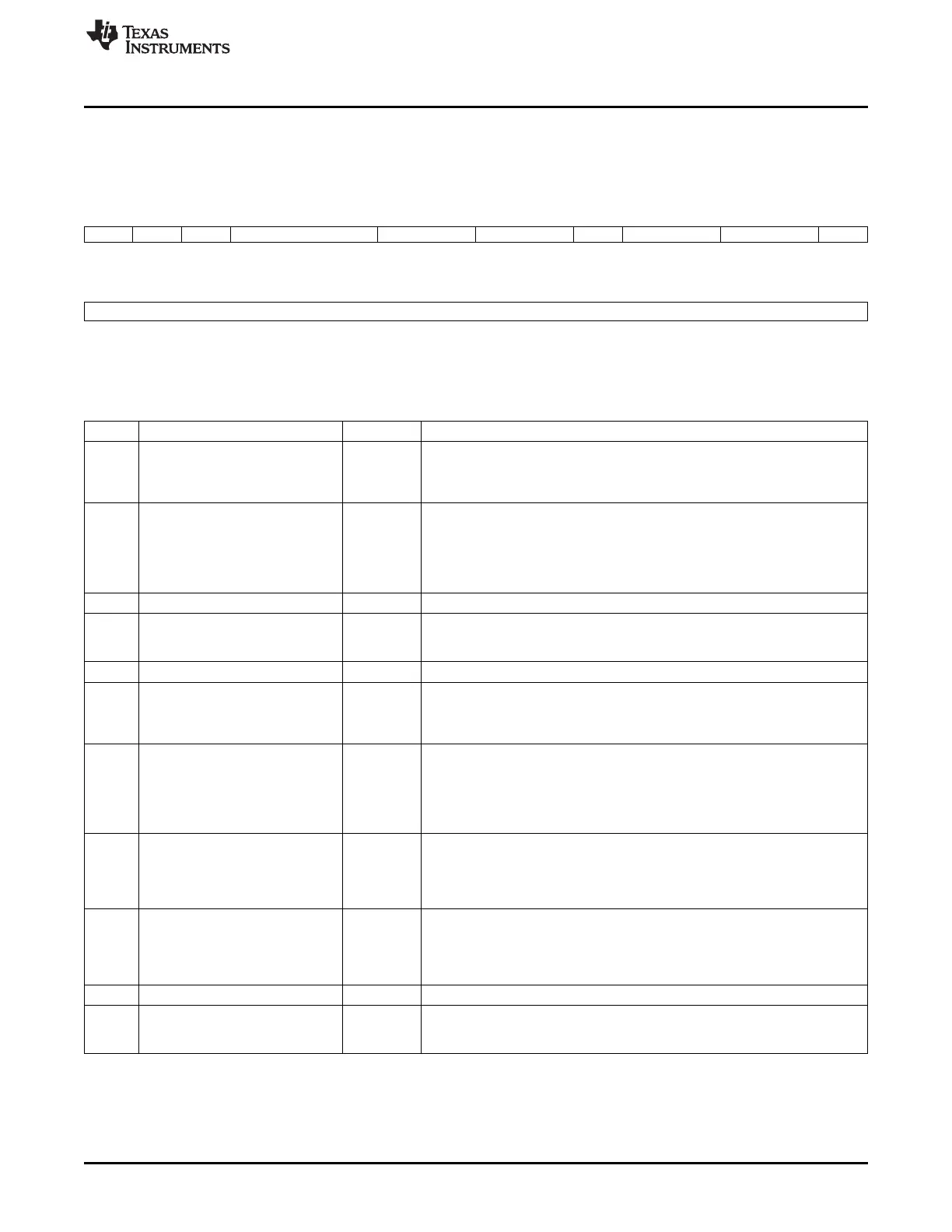

Table 14-252. MDIO Control Register (MDIOCONTROL) Field Descriptions

Bit Field Value Description

31 IDLE MDIO state machine IDLE. Set to 1 when the state machine is in the idle state.

0 State machine is not in idle state.

1 State machine is in idle state.

30 ENABLE Enable control. If the MDIO state machine is active at the time it is disabled, it

will complete the current operation before halting and setting the idle bit. If

using byte access, the enable bit has to be the last bit written in this register.

0 Disables the MDIO state machine.

1 Enable the MDIO state machine.

29 Reserved 0 Reserved.

28-24 HIGHEST_USER_CHANNEL 0-1Fh Highest user channel. This field specifies the highest user access channel that

is available in the module and is currently set to 1. This implies that the

MDIOUSERACCESS1 register is the highest available user access channel.

23-21 Reserved 0 Reserved.

20 PREAMBLE Preamble disable.

0 Standard MDIO preamble is used.

1 Disables this device from sending MDIO frame preambles.

19 FAULT Fault indicator. This bit is set to 1 if the MDIO pins fail to read back what the

device is driving onto them. This indicates a physical layer fault and the

module state machine is reset. Writing a 1 to it clears this bit.

0 No failure.

1 Physical layer fault; the MDIO state machine is reset.

18 FAULTENB Fault detect enable. This bit has to be set to 1 to enable the physical layer fault

detection.

0 Disables the physical layer fault detection.

1 Enables the physical layer fault detection.

17 INTTESTENB Interrupt test enable. This bit can be set to 1 to enable the host to set the

USERINT and LINKINT bits for test purposes.

0 Interrupt bits are not set.

1 Enables the host to set the USERINT and LINKINT bits for test purposes.

16 Reserved 0 Reserved.

15-0 CLKDIV 0-FFFFh Clock divider. This field specifies the division ratio between CLK and the

frequency of MDCLK. MDCLK is disabled when clkdiv is set to 0. MDCLK

frequency = clk frequency/(clkdiv+1).

14.5.10.3 PHY Acknowledge Status Register (MDIOALIVE)

The PHY acknowledge status register (MDIOALIVE) is shown in Figure 14-234 and described in Table 14-

253.

1475

SPRUH73H–October 2011–Revised April 2013 Ethernet Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...