www.ti.com

UART Registers

19.5.1.12 Line Status Register (LSR) - UART Mode

When the UART line status register (LSR) is read, LSR[4:2] reflect the error bits (BI, FE, PE) of the

character at the top of the RX FIFO (next character to be read). Therefore, reading the LSR and then

reading the RHR identifies errors in a character. Reading RHR updates BI, FE, and PE. LSR [7] is set

when there is an error anywhere in the RX FIFO and is cleared only when there are no more errors

remaining in the RX FIFO. The UART line status register (LSR) is shown in Figure 19-45 and described in

Table 19-41.

NOTE: Reading the LSR does not cause an increment of the RX FIFO read pointer. The RX FIFO

read pointer is incremented by reading the RHR. Reading LSR clears OE if set.

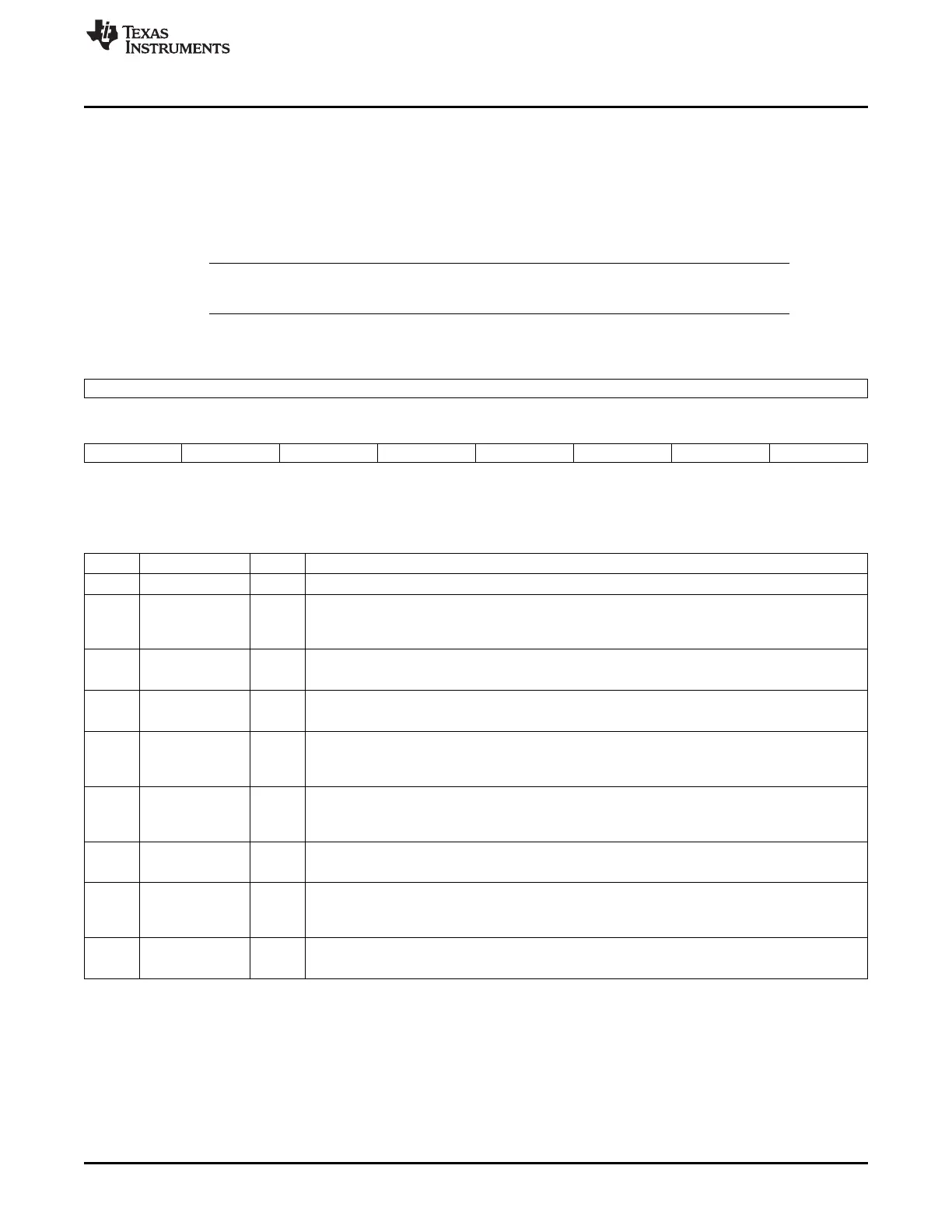

Figure 19-45. UART Line Status Register (LSR)

15 8

Reserved

R-0

7 6 5 4 3 2 1 0

RXFIFOSTS TXSRE TXFIFOE RXBI RXFE RXPE RXOE RXFIFOE

R-0 R-1 R-1 R-0 R-0 R-0 R-0 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

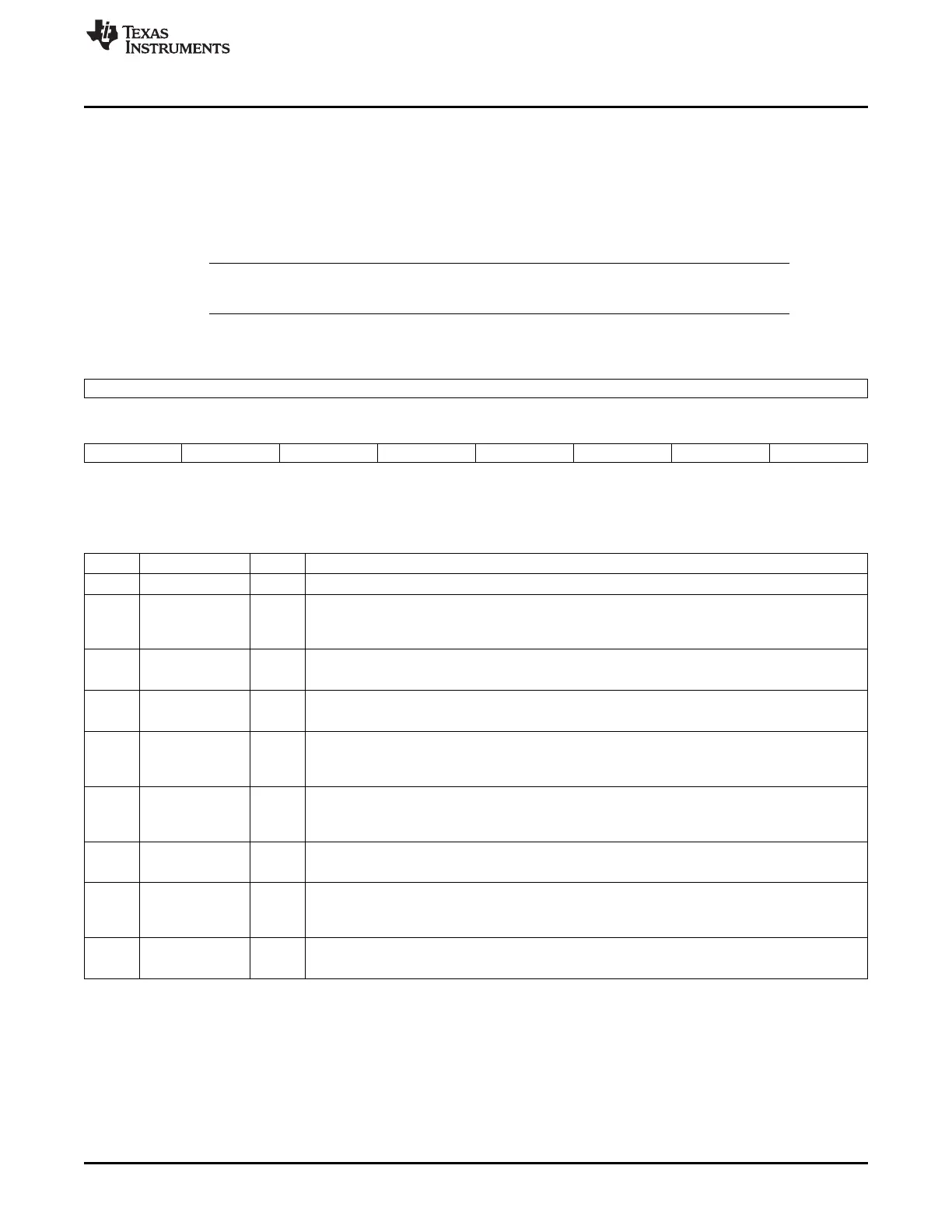

Table 19-41. UART Line Status Register (LSR) Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7 RXFIFOSTS 0 Normal operation.

1 At least one parity error, framing error, or break indication in the RX FIFO. Bit 7 is cleared when no

errors are present in the RX FIFO.

6 TXSRE 0 Transmitter hold (TX FIFO) and shift registers are not empty.

1 Transmitter hold (TX FIFO) and shift registers are empty.

5 TXFIFOE 0 Transmit hold register (TX FIFO) is not empty.

1 Transmit hold register (TX FIFO) is empty. The transmission is not necessarily completed.

4 RXBI 0 No break condition.

1 A break was detected while the data being read from the RX FIFO was being received (RX input

was low for one character + 1 bit time frame).

3 RXFE 0 No framing error in data being read from RX FIFO.

1 Framing error occurred in data being read from RX FIFO (received data did not have a valid stop

bit).

2 RXPE 0 No parity error in data being read from RX FIFO.

1 Parity error in data being read from RX FIFO.

1 RXOE 0 No overrun error.

1 Overrun error occurred. Set when the character held in the receive shift register is not transferred to

the RX FIFO. This case occurs only when receive FIFO is full.

0 RXFIFOE 0 No data in the receive FIFO.

1 At least one data character in the RX FIFO.

3517

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...