www.ti.com

Functional Description

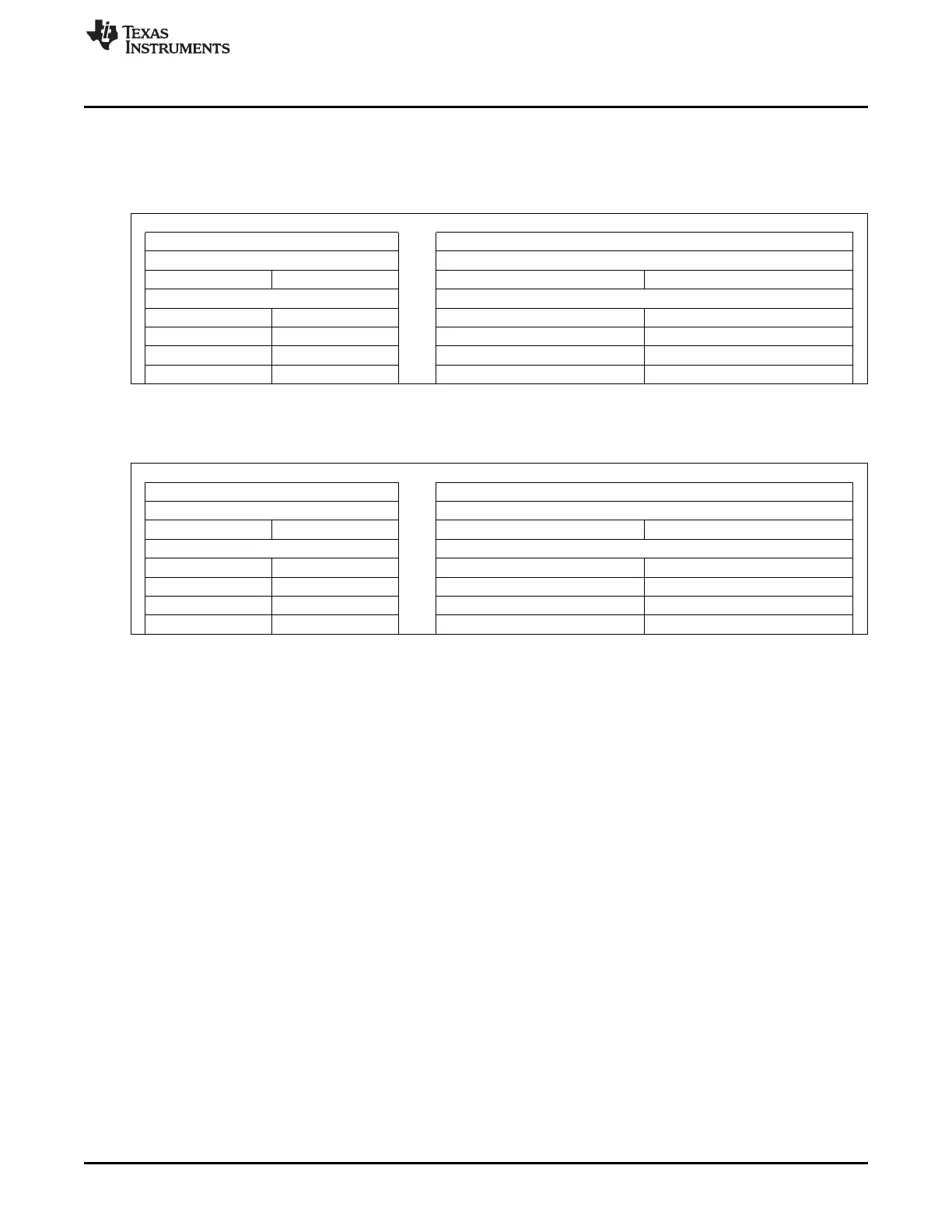

Figure 11-38. Ping-Pong Buffering for McASP Example Ping PaRAM Configuration

(a) EDMA Ping Parameters for Channel 15 at Set 65 Linked to Set 64

Parameter Contents Parameter

0010 D000h Channel Options Parameter (OPT)

McASP RX Register Channel Source Address (SRC)

0080h 0001h Count for 2nd Dimension (BCNT) Count for 1st Dimension (ACNT)

Channel Destination Address (DST) Channel Destination Address (DST)

0001h 0000h Destination BCNT Index (DSTBIDX) Source BCNT Index (SRCBIDX)

0080h 4800h BCNT Reload (BCNTRLD) Link Address (LINK)

0000h 0000h Destination CCNT Index (DSTCIDX) Source CCNT Index (SRCCIDX)

0000h 0001h Reserved Count for 3rd Dimension (CCNT)

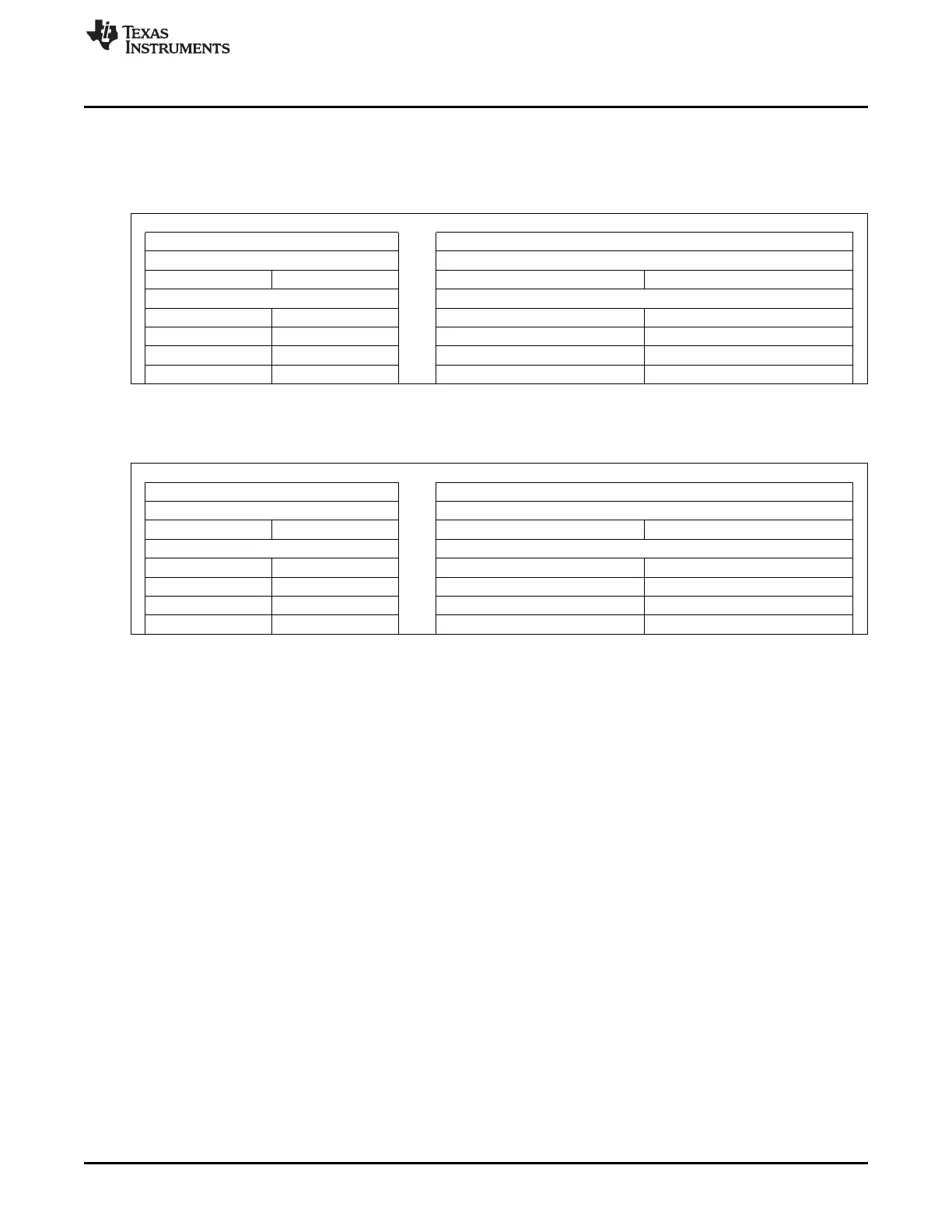

(b) EDMA Ping Parameters for Channel 12 at Set 67 Linked to Set 66

Parameter Contents Parameter

0010 C000h Channel Options Parameter (OPT)

Channel Source Address (SRC) Channel Source Address (SRC)

0080h 0001h Count for 2nd Dimension (BCNT) Count for 1st Dimension (ACNT)

McASP TX Register Channel Destination Address (DST)

0000h 0001h Destination BCNT Index (DSTBIDX) Source BCNT Index (SRCBIDX)

0080h 4840h BCNT Reload (BCNTRLD) Link Address (LINK)

0000h 0000h Destination CCNT Index (DSTCIDX) Source CCNT Index (SRCCIDX)

0000h 0001h Reserved Count for 3rd Dimension (CCNT)

11.3.19.4.5 Transfer Chaining Examples

The following examples explain the intermediate transfer complete chaining function.

11.3.19.4.5.1 Servicing Input/Output FIFOs with a Single Event

Many systems require the use of a pair of external FIFOs that must be serviced at the same rate. One

FIFO buffers data input, and the other buffers data output. The EDMA3 channels that service these FIFOs

can be set up for AB-synchronized transfers. While each FIFO is serviced with a different set of

parameters, both can be signaled from a single event. For example, an external interrupt pin can be tied

to the status flags of one of the FIFOs. When this event arrives, the EDMA3 needs to perform servicing for

both the input and output streams. Without the intermediate transfer complete chaining feature this would

require two events, and thus two external interrupt pins. The intermediate transfer complete chaining

feature allows the use of a single external event (for example, a GPIO event). Figure 11-39 shows the

EDMA3 setup and illustration for this example.

A GPIO event (in this case, GPINT0) triggers an array transfer. Upon completion of each intermediate

array transfer of channel 48, intermediate transfer complete chaining sets the E8 bit (specified by TCC of

8) in the chained event register (CER) and provides a synchronization event to channel 8. Upon

completion of the last array transfer of channel 48, transfer complete chaining—not intermediate transfer

complete chaining—sets the E8 bit in CER (specified by TCCMODE:TCC) and provides a synchronization

event to channel 8. The completion of channel 8 sets the I8 bit (specified by TCCMODE:TCC) in the

interrupt pending register (IPR), which can generate an interrupt to the CPU, if the I8 bit in the interrupt

enable register (IER) is set.

933

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...