www.ti.com

McASP Registers

22.4.1.30 Transmit High-Frequency Clock Control Register (AHCLKXCTL)

The transmit high-frequency clock control register (AHCLKXCTL) configures the transmit high-frequency

master clock (AHCLKX) and the transmit clock generator. The AHCLKXCTL is shown in Figure 22-68 and

described in Table 22-41.

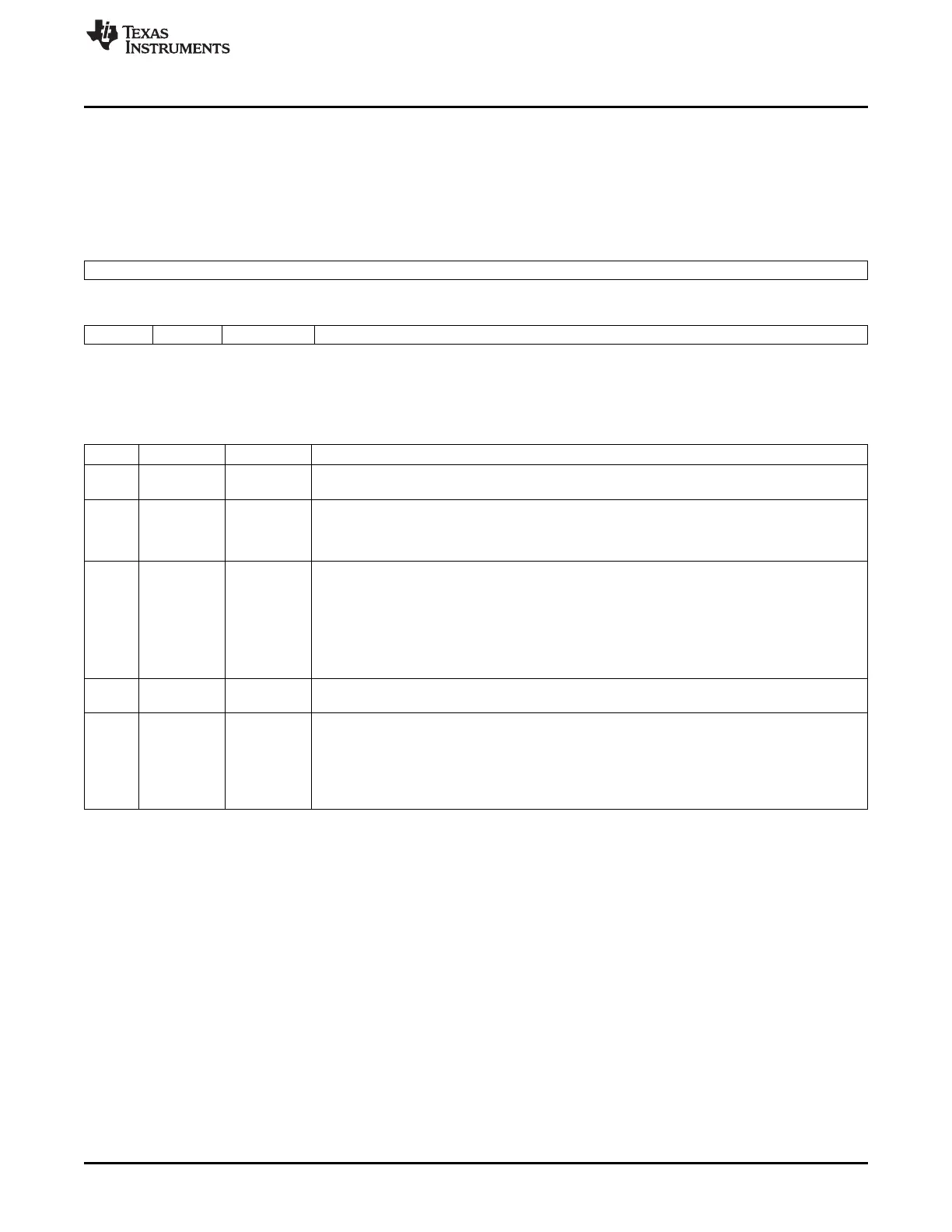

Figure 22-68. Transmit High-Frequency Clock Control Register (AHCLKXCTL)

31 16

Reserved

R-0

15 14 13 12 11 0

HCLKXM HCLKXP Reserved HCLKXDIV

R/W-1 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

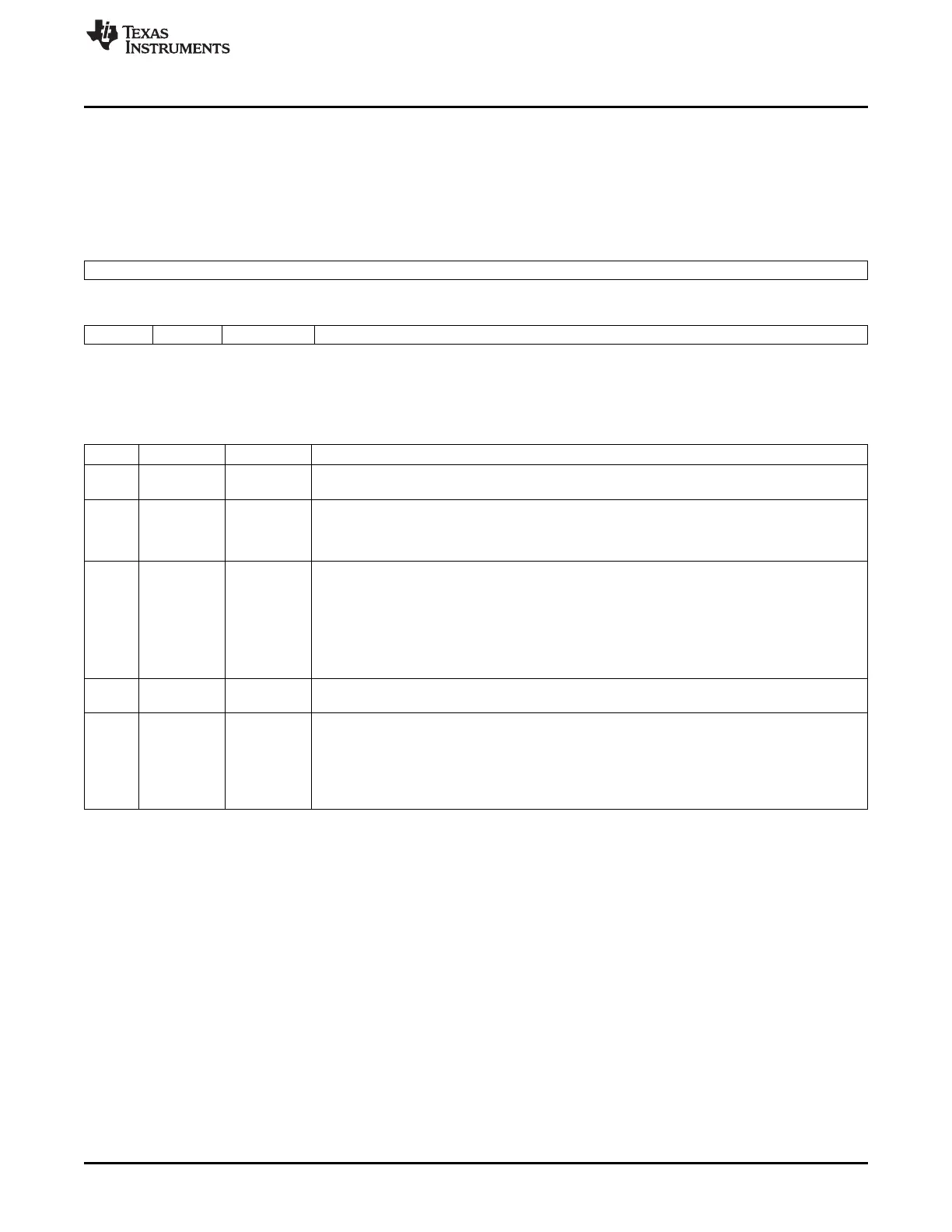

Table 22-41. Transmit High-Frequency Clock Control Register (AHCLKXCTL) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reserved. The reserved bit location always returns the default value. A value written to this field

has no effect. If writing to this field, always write the default value for future device compatibility.

15 HCLKXM Transmit high-frequency clock source bit.

0 External transmit high-frequency clock source from AHCLKX pin.

1 Internal transmit high-frequency clock source from output of programmable high clock divider.

14 HCLKXP Transmit bitstream high-frequency clock polarity select bit.

0 AHCLKX is not inverted before programmable bit clock divider. In the special case where the

transmit bit clock (ACLKX) is internally generated and the programmable bit clock divider is set to

divide-by-1 (CLKXDIV = 0 in ACLKXCTL), AHCLKX is directly passed through to the ACLKX pin.

1 AHCLKX is inverted before programmable bit clock divider. In the special case where the transmit

bit clock (ACLKX) is internally generated and the programmable bit clock divider is set to divide-

by-1 (CLKXDIV = 0 in ACLKXCTL), AHCLKX is directly passed through to the ACLKX pin.

13-12 Reserved 0 Reserved. The reserved bit location always returns the default value. A value written to this field

has no effect. If writing to this field, always write the default value for future device compatibility.

11-0 HCLKXDIV 0-FFFh Transmit high-frequency clock divide ratio bits determine the divide-down ratio from AUXCLK to

AHCLKX.

0 Divide-by-1.

1h Divide-by-2.

2h-FFFh Divide-by-3 to divide-by-4096.

3867

SPRUH73H–October 2011–Revised April 2013 Multichannel Audio Serial Port (McASP)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...