Ethernet Subsystem Registers

www.ti.com

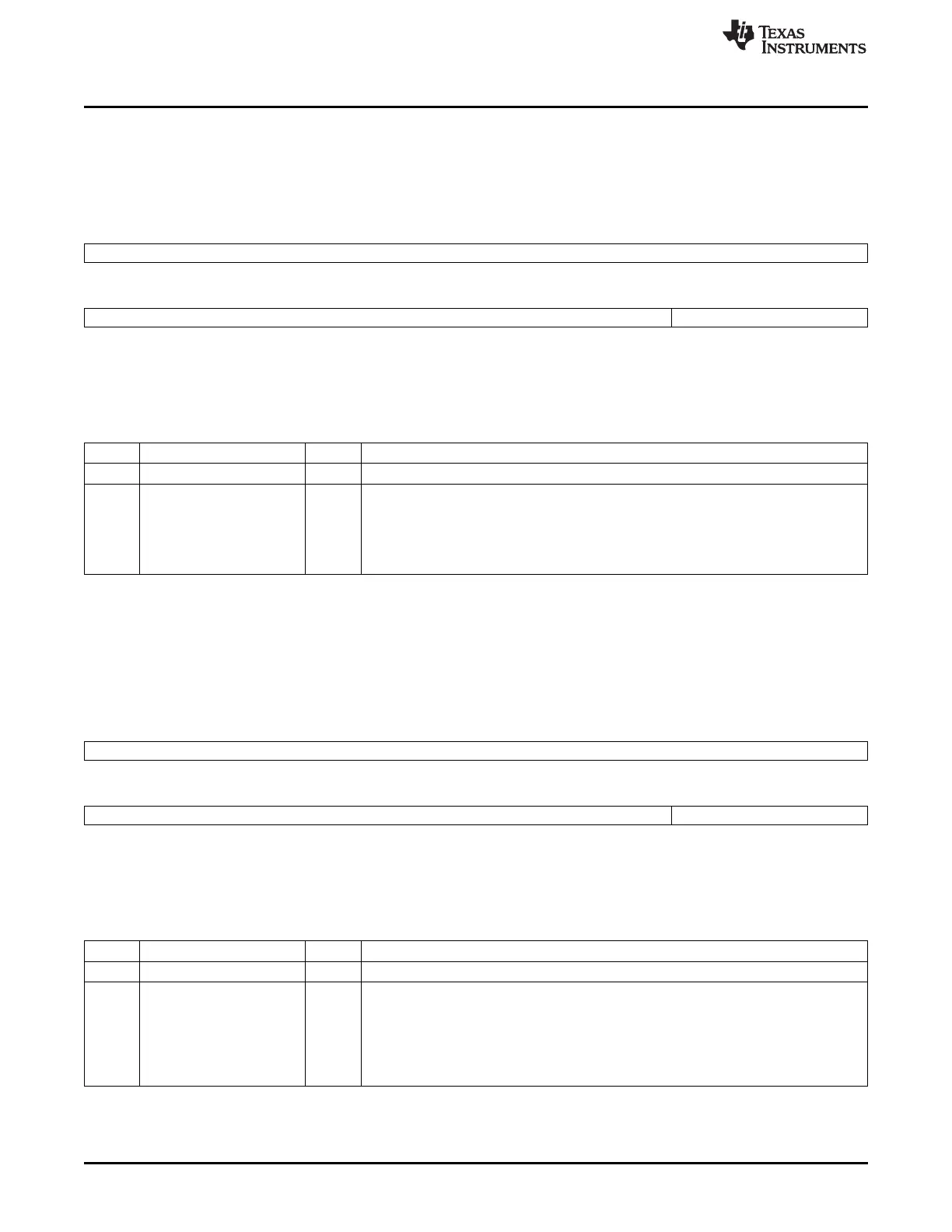

14.5.10.7 MDIO User Command Complete Interrupt Register (Raw Value) (MDIOUSERINTRAW)

The MDIO user command complete interrupt register (Raw Value) (MDIOUSERINTRAW) is shown in

Figure 14-238 and described in Table 14-257.

Figure 14-238. MDIO User Command Complete Interrupt Register (Raw Value) (MDIOUSERINTRAW)

31 16

Reserved

R-0x0

15 2 1 0

Reserved USERINTRAW

R-0x0 RWC-0x0

LEGEND: RWC = Read/Write/Clear; R = Read only; -n = value after reset

Table 14-257. MDIO User Command Complete Interrupt Register (Raw Value) (MDIOUSERINTRAW)

Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reserved.

1-0 USERINTRAW 0-3h Raw value of MDIO user command complete event for the MDIOUSERACCESS1 register

through the MDIOUSERACCESS0 register, respectively. When asserted 1, a bit indicates

that the previously scheduled PHY read or write command using that particular

MDIOUSERACCESSn register has completed. Writing a 1 will clear the event and writing

0 has no effect. If the INTTESTENB bit in the MDIOCONTROL register is set, the host

may set the USERINTRAW bits to a 1. This mode may be used for test purposes.

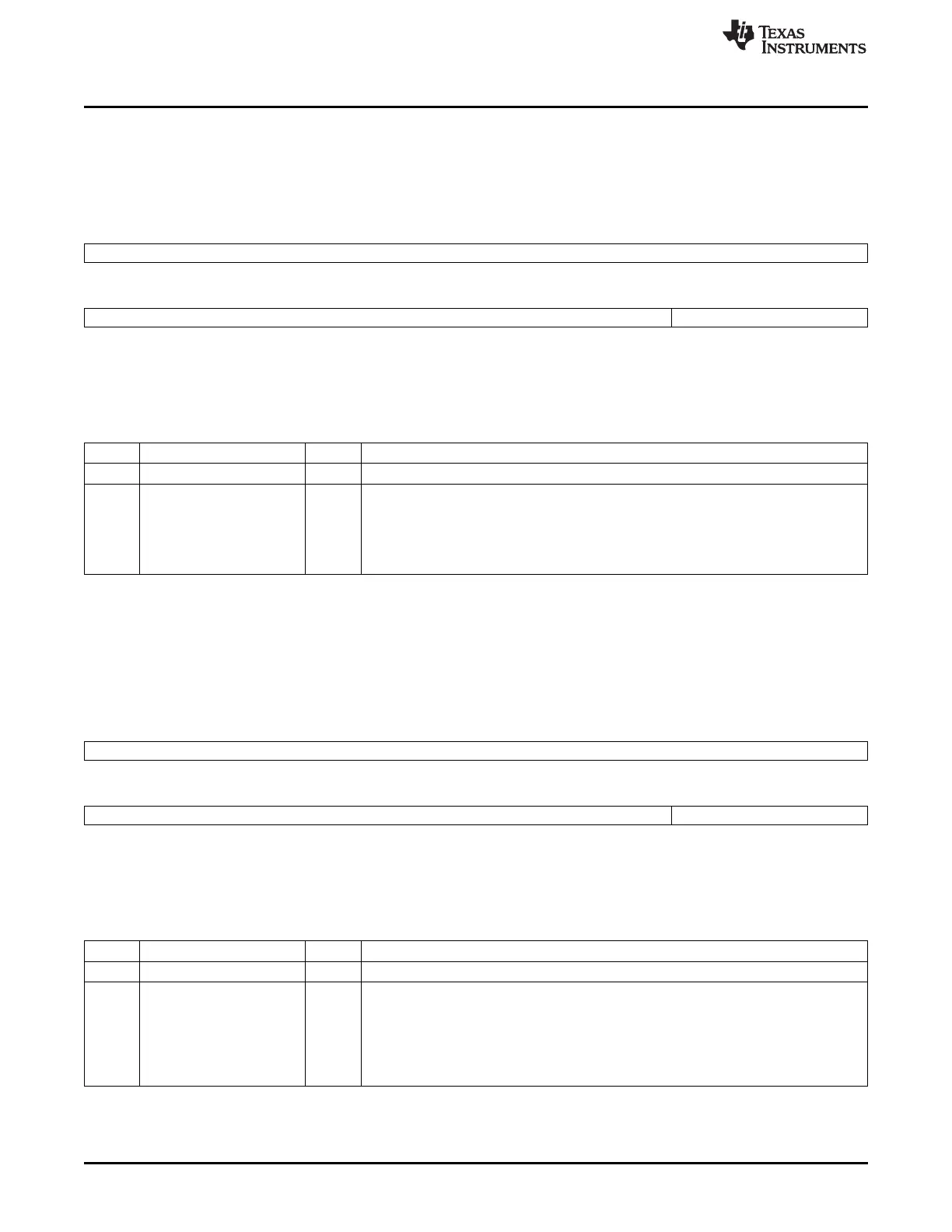

14.5.10.8 MDIO User Command Complete Interrupt Register (Masked Value) (MDIOUSERINTMASKED)

The MDIO user command complete interrupt register (Masked Value) (MDIOUSERINTMASKED) is shown

in Figure 14-239 and described in Table 14-258.

Figure 14-239. MDIO User Command Complete Interrupt Register (Masked Value)

(MDIOUSERINTMASKED)

31 16

Reserved

R-0x0

15 2 1 0

Reserved USERINTMASKED

R-0x0 RWC-0x0

LEGEND: RWC = Read/Write/Clear; R = Read only; -n = value after reset

Table 14-258. MDIO User Command Complete Interrupt Register (Masked Value)

(MDIOUSERINTMASKED) Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reserved.

1-0 USERINTMASKED 0-3h Masked value of MDIO user command complete interrupt for the MDIOUSERACCESS1

register through the MDIOUSERACCESS0 register, respectively. When asserted 1, a bit

indicates that the previously scheduled PHY read or write command using that particular

MDIOUSERACCESSn register has completed and the corresponding

USERINTMASKSET bit is set to 1. Writing a 1 will clear the interrupt and writing 0 has no

effect. If the INTTESTENB bit in the MDIOCONTROL register is set, the host may set the

USERINTMASKED bits to a 1. This mode may be used for test purposes.

1478

Ethernet Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...