www.ti.com

McASP Registers

22.4.1.23 Receive Clock Check Control Register (RCLKCHK)

The receive clock check control register (RCLKCHK) configures the receive clock failure detection circuit.

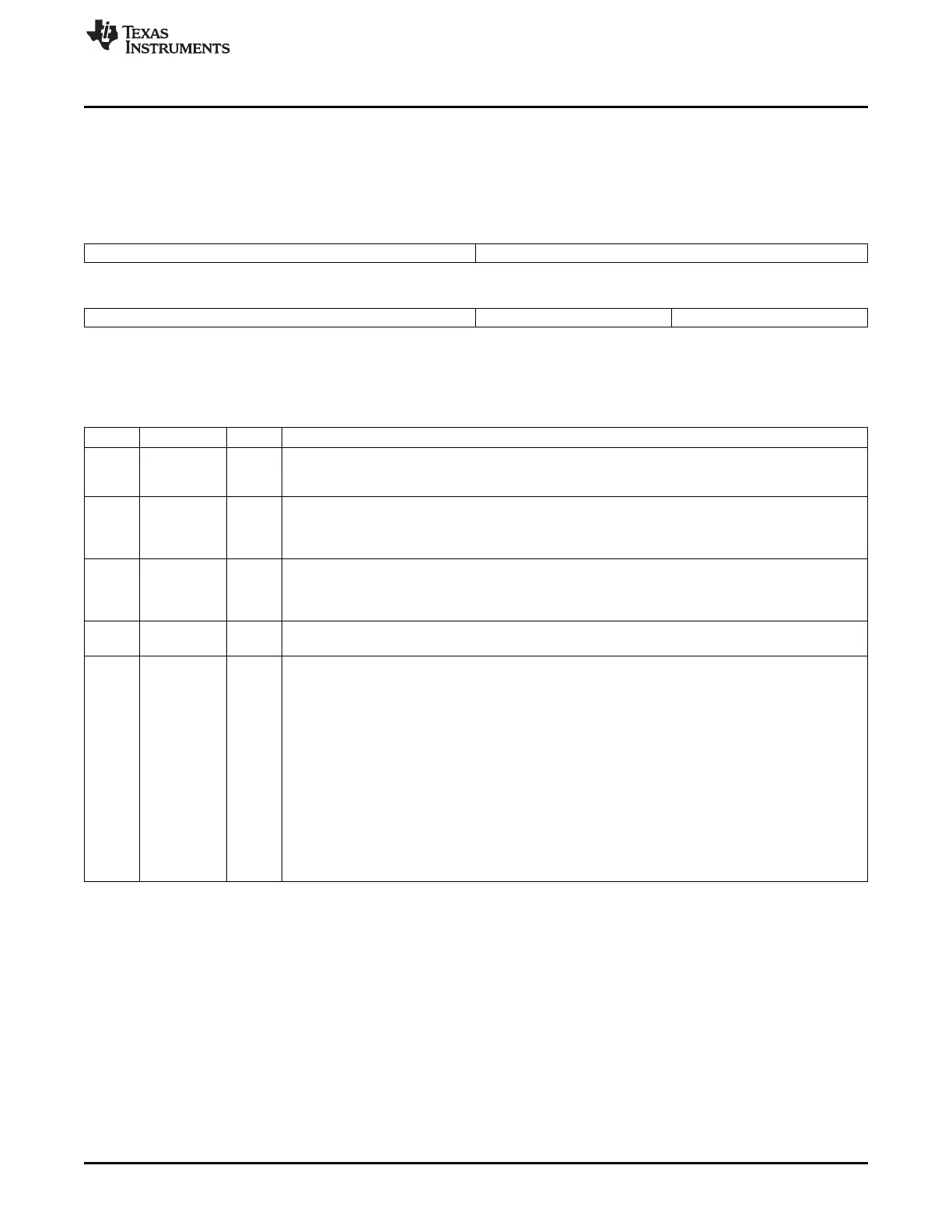

The RCLKCHK is shown in Figure 22-61 and described in Table 22-34.

Figure 22-61. Receive Clock Check Control Register (RCLKCHK)

31 24 23 16

RCNT RMAX

R-0 R/W-0

15 8 7 4 3 0

RMIN Reserved RPS

R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

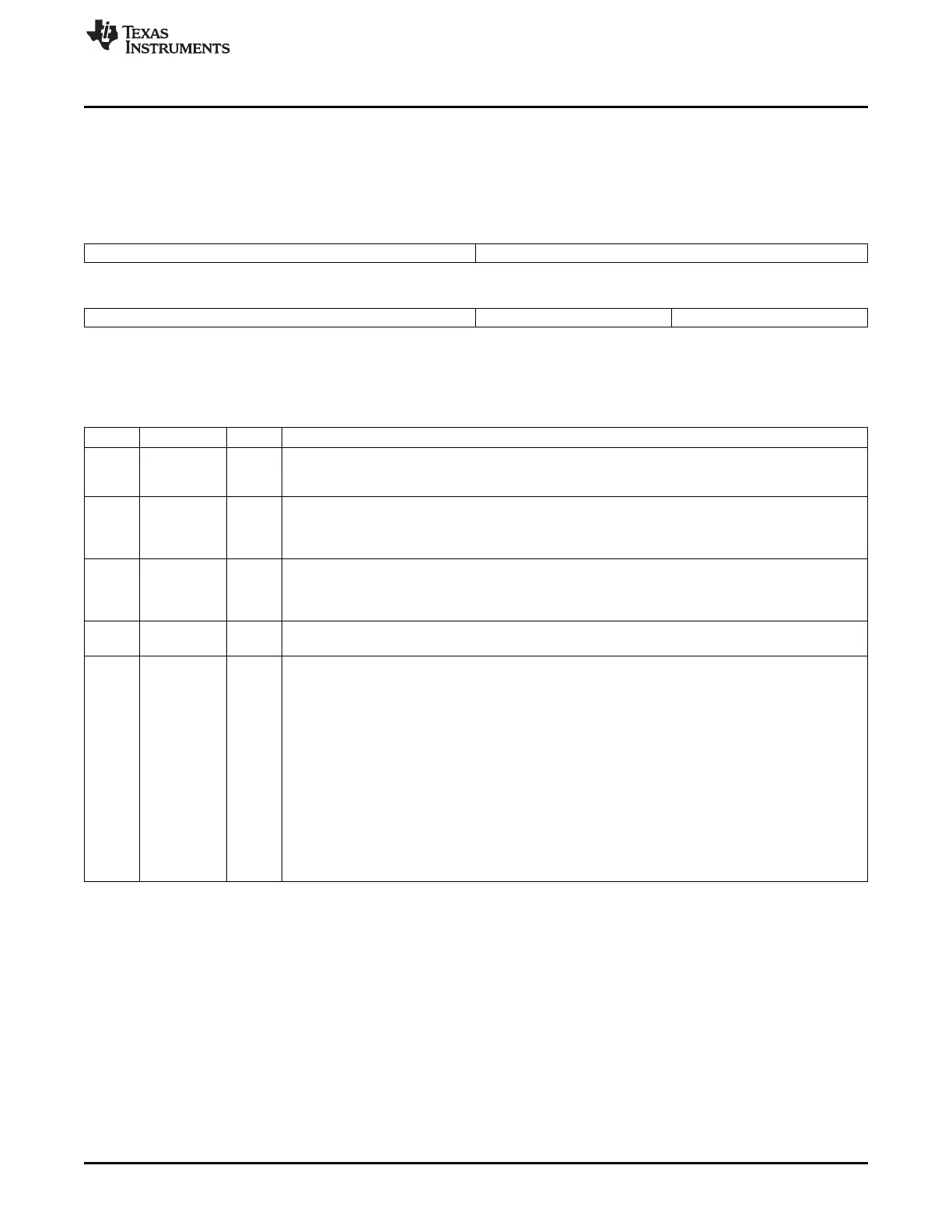

Table 22-34. Receive Clock Check Control Register (RCLKCHK) Field Descriptions

Bit Field Value Description

31-24 RCNT 0-FFh Receive clock count value (from previous measurement). The clock circuit continually counts the

number of system clocks for every 32 receive high-frequency master clock (AHCLKR) signals, and

stores the count in RCNT until the next measurement is taken.

23-16 RMAX 0-FFh Receive clock maximum boundary. This 8-bit unsigned value sets the maximum allowed boundary for

the clock check counter after 32 receive high-frequency master clock (AHCLKR) signals have been

received. If the current counter value is greater than RMAX after counting 32 AHCLKR signals,

RCKFAIL in RSTAT is set. The comparison is performed using unsigned arithmetic.

15-8 RMIN 0-FFh Receive clock minimum boundary. This 8-bit unsigned value sets the minimum allowed boundary for the

clock check counter after 32 receive high-frequency master clock (AHCLKR) signals have been

received. If RCNT is less than RMIN after counting 32 AHCLKR signals, RCKFAIL in RSTAT is set. The

comparison is performed using unsigned arithmetic.

7-4 Reserved 0 Reserved. The reserved bit location always returns the default value. A value written to this field has no

effect. If writing to this field, always write the default value for future device compatibility.

3-0 RPS 0-Fh Receive clock check prescaler value.

0 McASP system clock divided by 1.

1h McASP system clock divided by 2.

2h McASP system clock divided by 4.

3h McASP system clock divided by 8.

4h McASP system clock divided by 16.

5h McASP system clock divided by 32.

6h McASP system clock divided by 64.

7h McASP system clock divided by 128.

8h McASP system clock divided by 256.

9h-Fh Reserved.

3859

SPRUH73H–October 2011–Revised April 2013 Multichannel Audio Serial Port (McASP)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...