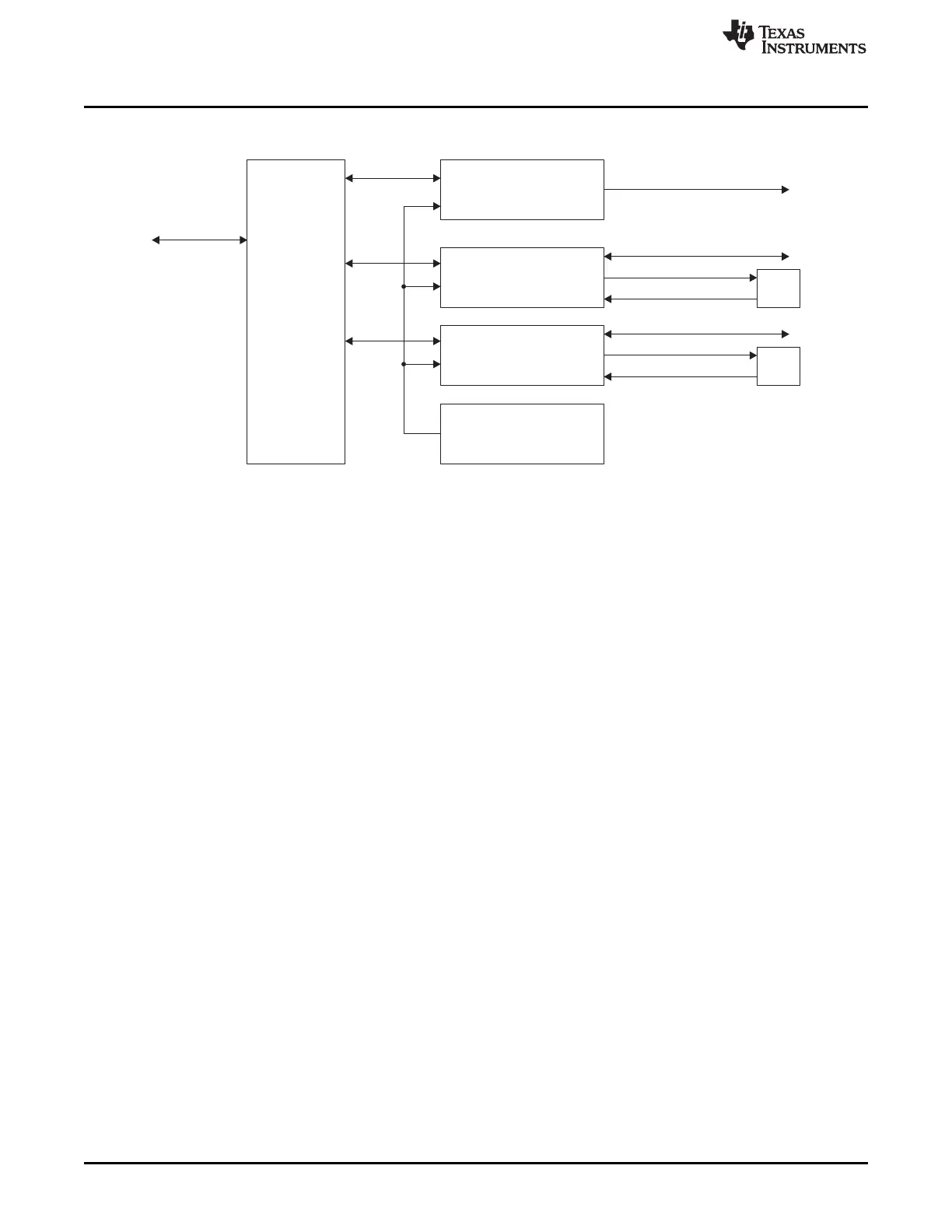

DDR2/3/mDDR

Memory

Controller

data[15:8] to/from DDR

fifo_we_in

fifo_we_out

Data Macro 1

IO 1

data[7:0] to/from DDR

fifo_we_in

fifo_we_out

Data Macro 0

IO 0

To DDR

Command Macros

VTP Macro

cmd/addr

data

data

p/n

128-bit

OCP

Where

fifo_we_out = DQS enable output for timing match between DQS and system (Memory) clock.

fifo_we_in = DQS enable input for timing match between DQS and system (Memory) clock.

EMIF

www.ti.com

Figure 7-89. DDR2/3/mDDR Subsystem Block Diagram

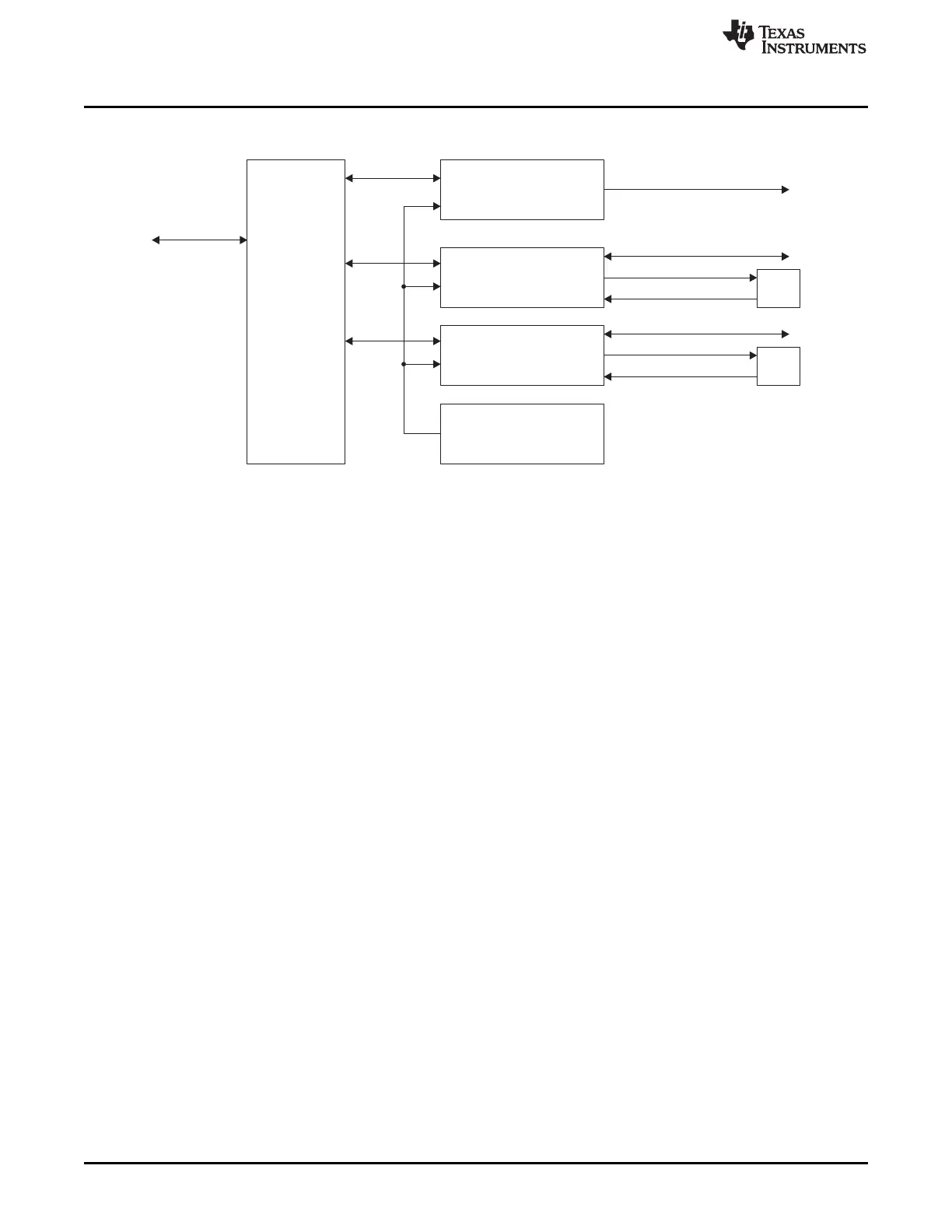

7.3.3.3.1 DDR2/3/mDDR Memory Controller Interface

To move data efficiently from on-chip resources to external DDR2/3/mDDR SDRAM device, the

DDR2/3/mDDR memory controller makes use of a command FIFO, a write data FIFO, a return command

FIFO, and two Read Data FIFOs. Purpose of each FIFO is described below.

Figure 7-90 shows the block diagram of the DDR2/3/mDDR memory controller FIFOs. Commands, write

data, and read data arrive at the DDR2 memory controller parallel to each other. The same peripheral bus

is used to write and read data from external memory as well as internal memory-mapped registers.

406

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...