LCD Registers

www.ti.com

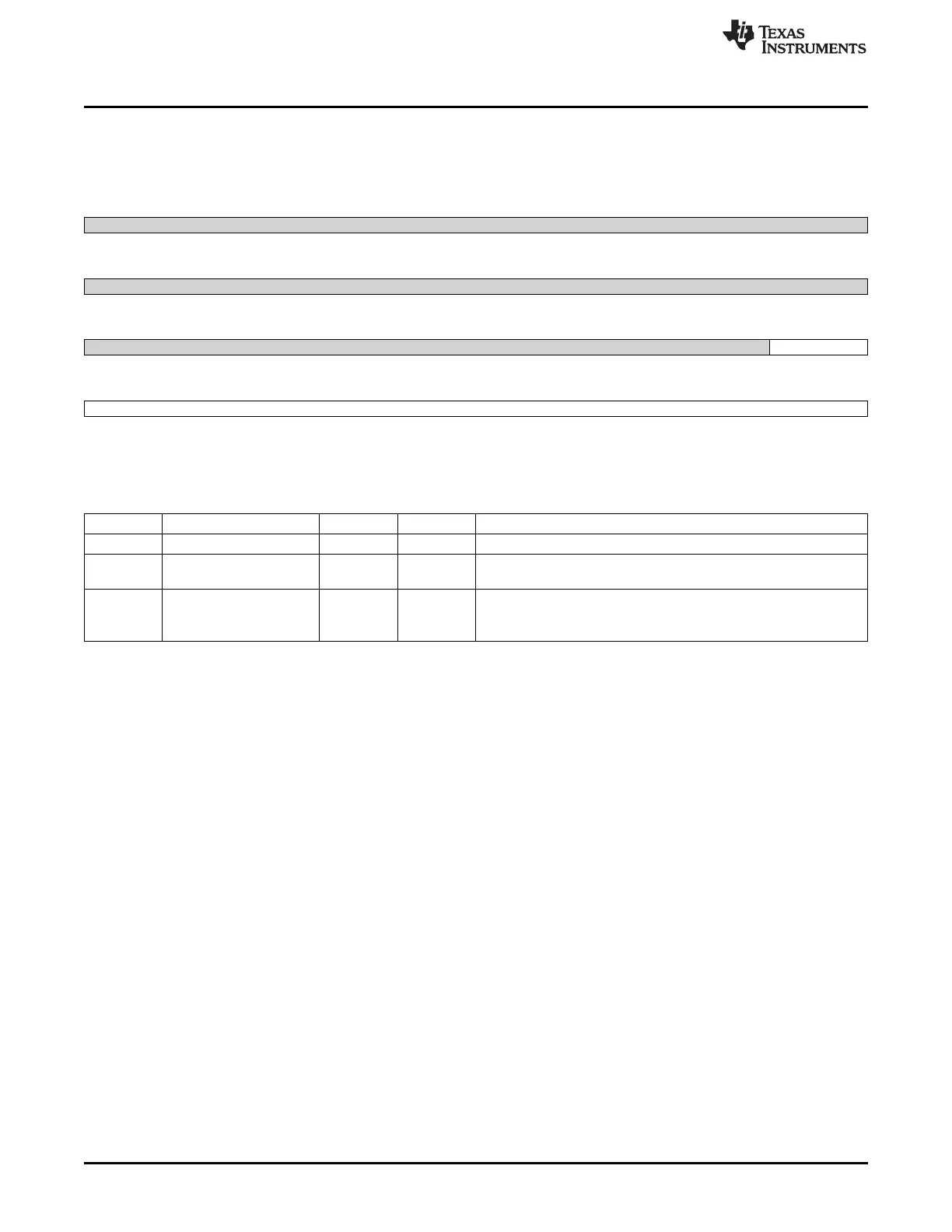

13.5.15 RASTER_SUBPANEL2 Register (offset = 3Ch) [reset = 0h]

RASTER_SUBPANEL2 is shown in Figure 13-33 and described in Table 13-28.

Figure 13-33. RASTER_SUBPANEL2 Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved lppt_b10

R-0h R/W-0h

7 6 5 4 3 2 1 0

dpdmsb

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

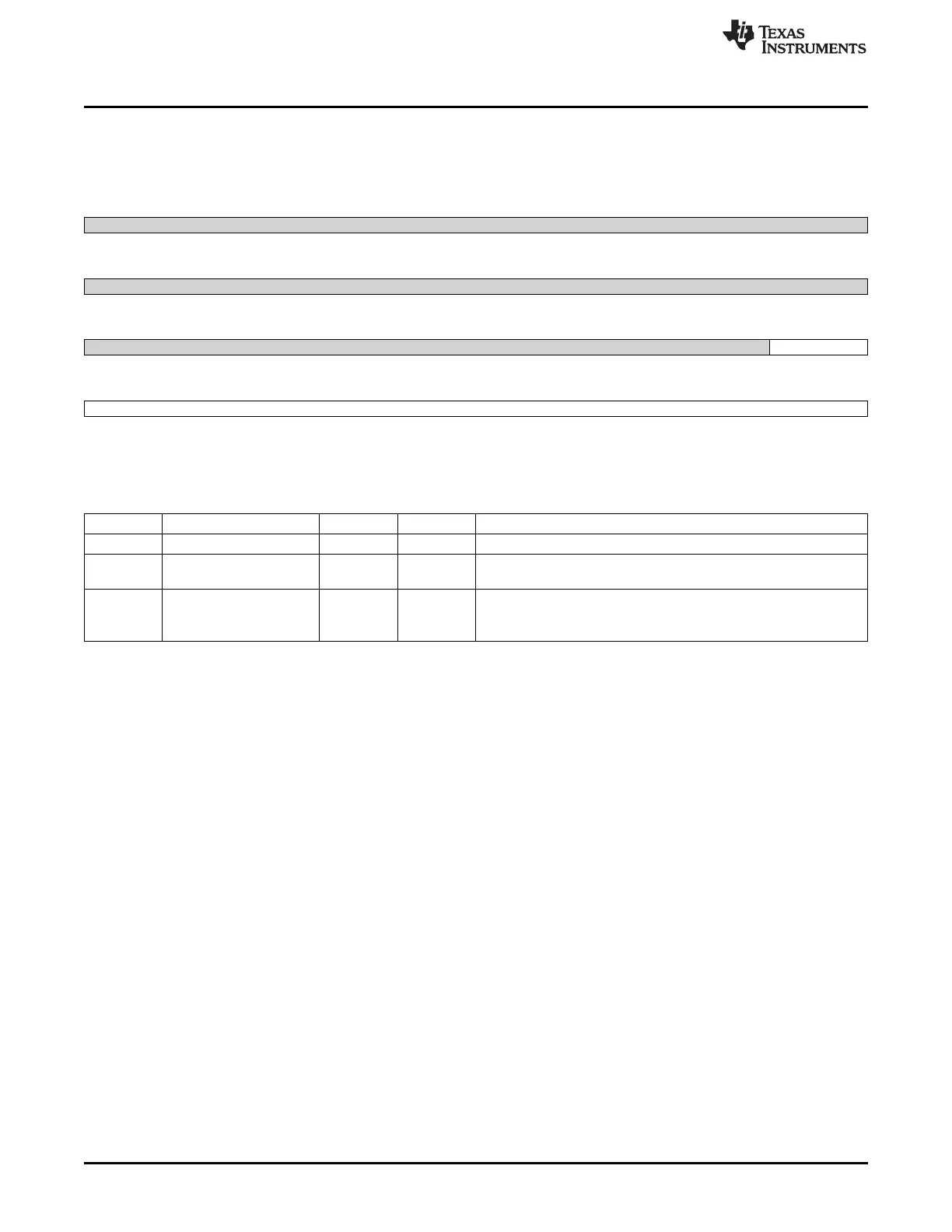

Table 13-28. RASTER_SUBPANEL2 Register Field Descriptions

Bit Field Type Reset Description

31-9 Reserved R 0h

8 lppt_b10 R/W 0h Lines Per Panel Threshold Bit 10 This register is Bit 10 of the lppt

field in RASTER_SUBPANEL

7-0 dpdmsb R/W 0h

Default Pixel Data MSB [23:16] DPD defines the default value of the

pixel data sent to the panel for the lines until LPPT is reached or

after passing the LPPT

1146

LCD Controller SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...