USB Registers

www.ti.com

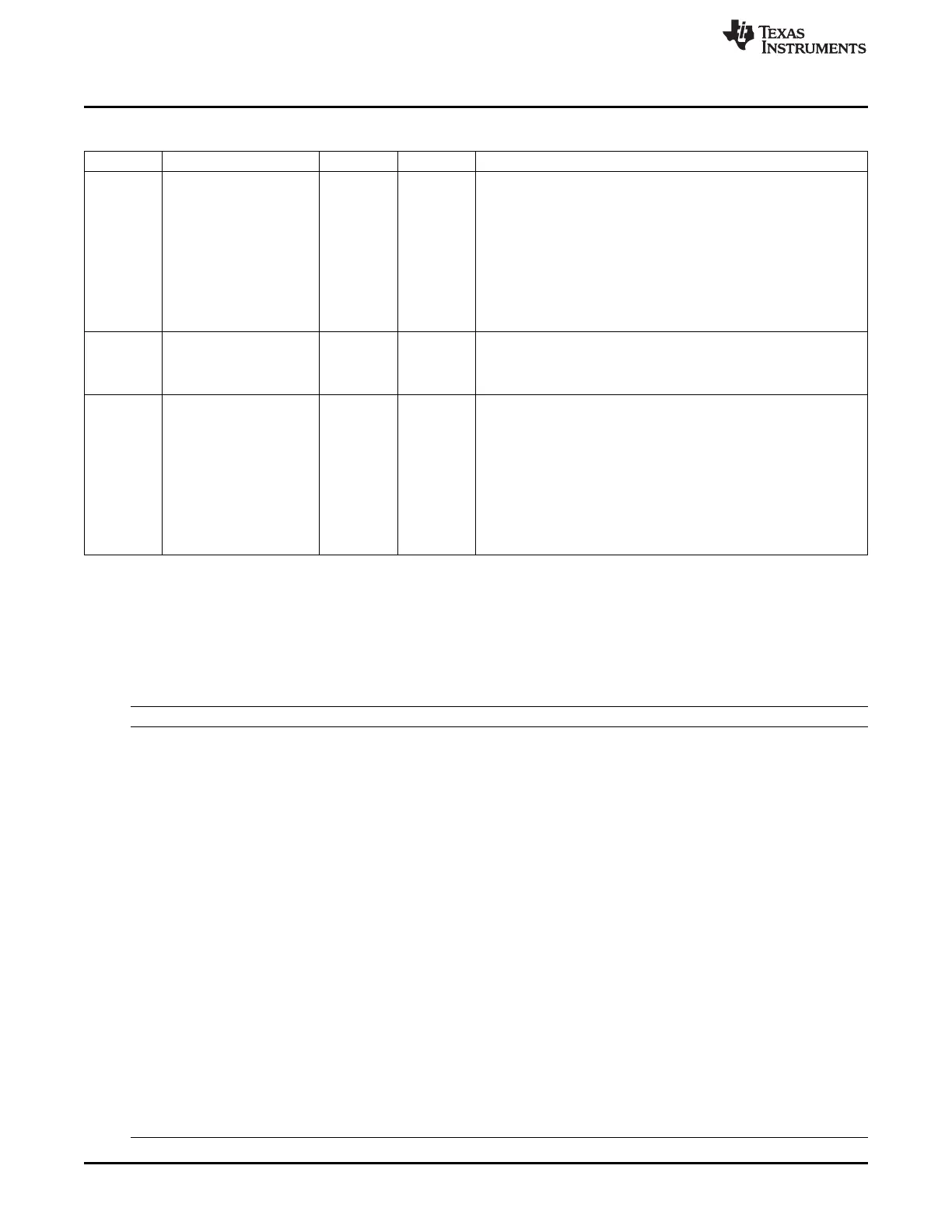

Table 16-289. WORD0 to WORD63 Register Field Descriptions (continued)

Bit Field Type Reset Description

12-8 ENTRY1_CHANNEL R/W This field indicates the channel number that is to be given an

opportunity to transfer data.

If this is a Tx entry, the DMA will be presented with a scheduling

credit for that exact Tx channel.

If this is an Rx entry, the DMA will be presented with a scheduling

credit for the Rx FIFO that is associated with this channel.

For Rx FIFOs which carry traffic for more than 1 Rx DMA channel,

the exact channel number that is given in the Rx credit will actually

be the channel number which is currently on the head element of

that Rx FIFO, which is not necessarily the channel number given in

the scheduler table entry.

7 ENTRY0_RXTX W 0h This bit indicates if this entry is for a Tx or an Rx channel and is

encoded as follows:

0 = Tx Channel

1 = Rx Channel

4-0 ENTRY0_CHANNEL R/W This field indicates the channel number that is to be given an

opportunity to transfer data.

If this is a Tx entry, the DMA will be presented with a scheduling

credit for that exact Tx channel.

If this is an Rx entry, the DMA will be presented with a scheduling

credit for the Rx FIFO that is associated with this channel.

For Rx FIFOs which carry traffic for more than 1 Rx DMA channel,

the exact channel number that is given in the Rx credit will actually

be the channel number which is currently on the head element of

that Rx FIFO, which is not necessarily the channel number given in

the scheduler table entry.

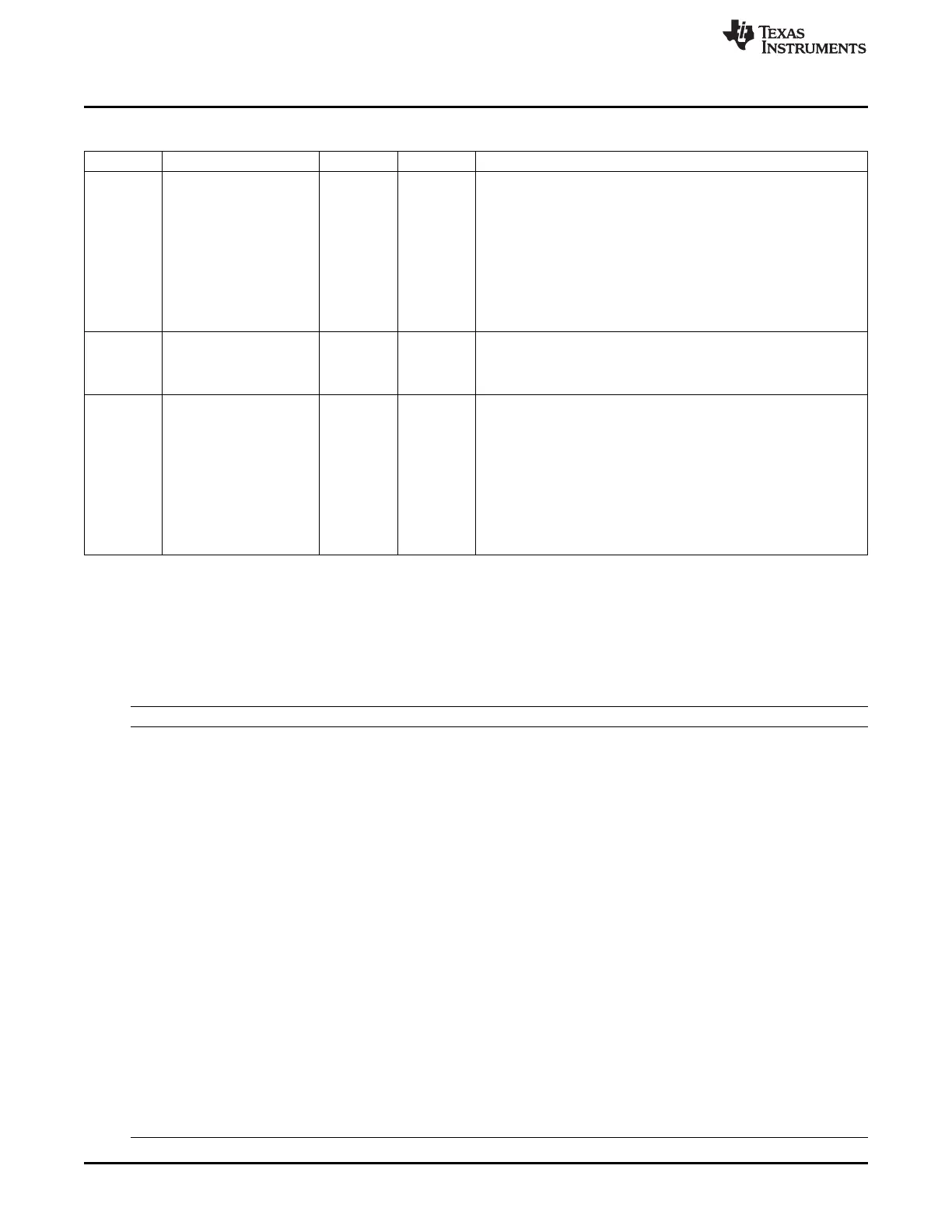

16.5.7 QUEUE_MGR Registers

Table 16-290 lists the memory-mapped registers for the QUEUE_MGR. All register offset addresses not

listed in Table 16-290 should be considered as reserved locations and the register contents should not be

modified.

Table 16-290. QUEUE_MGR REGISTERS

Offset Acronym Register Name Section

0h QMGRREVID Section 16.5.7.1

8h QMGRRST Section 16.5.7.2

20h FDBSC0 Section 16.5.7.3

24h FDBSC1 Section 16.5.7.4

28h FDBSC2 Section 16.5.7.5

2Ch FDBSC3 Section 16.5.7.6

30h FDBSC4 Section 16.5.7.7

34h FDBSC5 Section 16.5.7.8

38h FDBSC6 Section 16.5.7.9

3Ch FDBSC7 Section 16.5.7.10

80h LRAM0BASE Section 16.5.7.11

84h LRAM0SIZE Section 16.5.7.12

88h LRAM1BASE Section 16.5.7.13

90h PEND0 Section 16.5.7.14

94h PEND1 Section 16.5.7.15

98h PEND2 Section 16.5.7.16

9Ch PEND3 Section 16.5.7.17

A0h PEND4 Section 16.5.7.18

1000h QMEMRBASE0 Section 16.5.7.19

1004h QMEMCTRL0 Section 16.5.7.20

2084

Universal Serial Bus (USB) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...