GPMC

www.ti.com

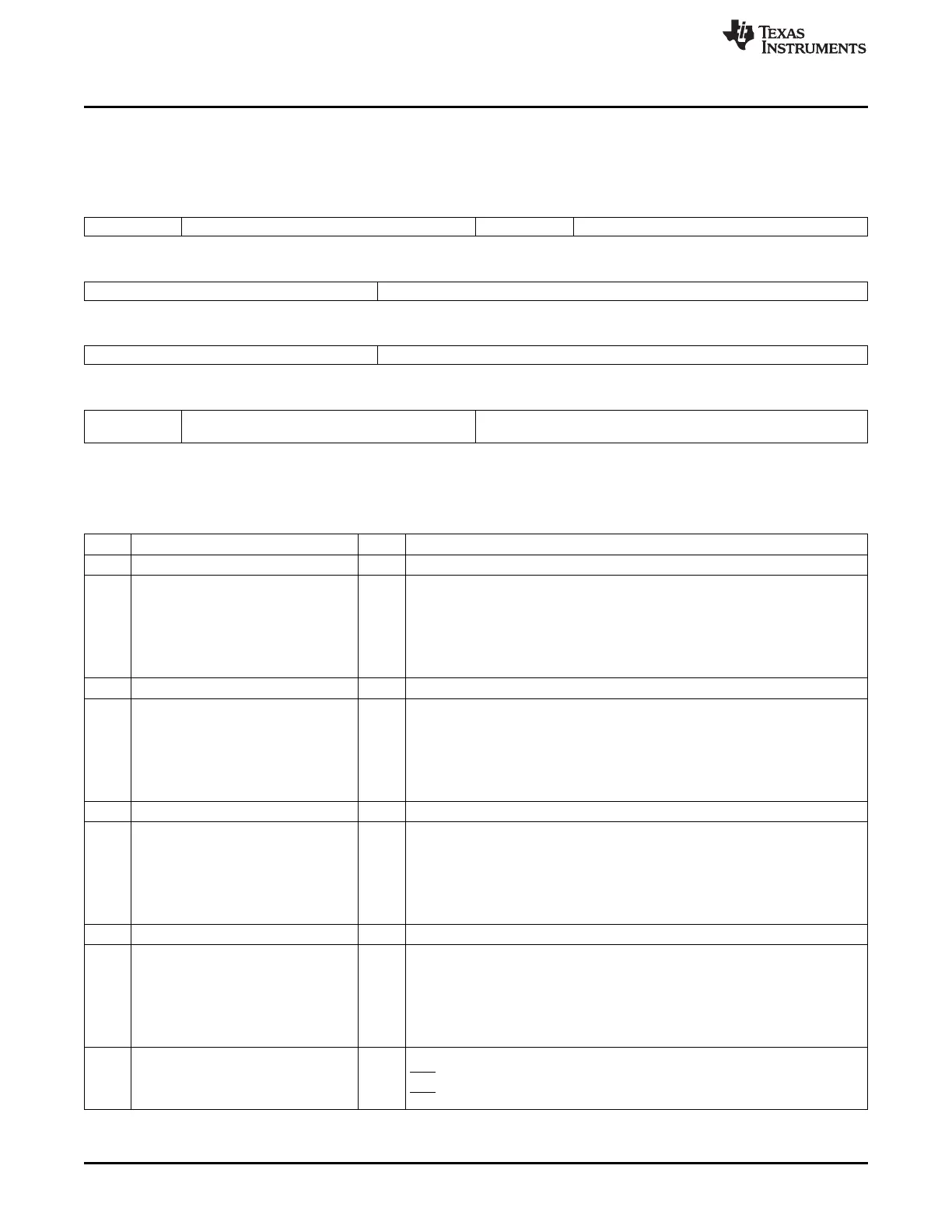

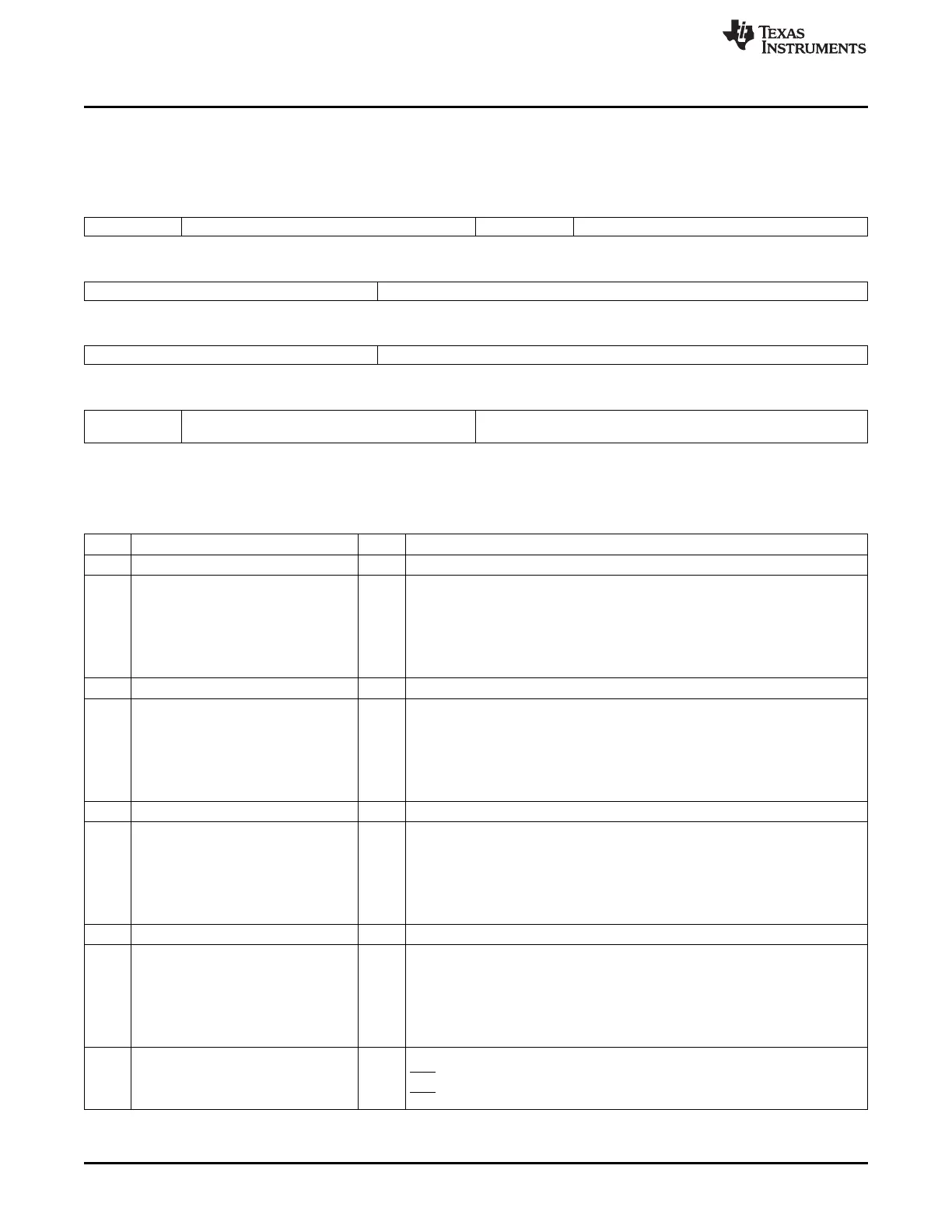

7.1.5.13 GPMC_CONFIG3_i

ADV# signal timing parameter configuration.

Figure 7-63. GPMC_CONFIG3_i

31 30 28 27 26 24

Reserved ADVAADMUXWROFFTIME Reserved ADVAADMUXRDOFFTIME

R-0 R/W-0 R-0 R/W-0

23 21 20 16

Reserved ADVWROFFTIME

R/W-0 R/W-0

15 13 12 8

Reserved ADVRDOFFTIME

R-0 R/W-0

7 6 4 3 0

ADVEXTRA ADVAADMUXONTIME ADVONTIME

DELAY

R/W-0 R/W-0 R/W-0

LEGEND: R = Read only; W1C = Write 1 to clear bit; -n = value after reset

Table 7-67. GPMC_CONFIG3_i Field Descriptions

Bit Field Value Description

31 Reserved 0 Reserved

30-28 ADVAADMUXWROFFTIME ADV# de-assertion for first address phase when using the AAD-Mux protocol

0 0 GPMC_FCLK cycle

1h 1 GPMC_FCLK cycle

⋮ ⋮

7h 7 GPMC_FCLK cycles

27 Reserved 0 Reserved

26-24 ADVAADMUXRDOFFTIME ADV# assertion for first address phase when using the AAD-Mux protocol

0 0 GPMC_FCLK cycle

1h 1 GPMC_FCLK cycle

⋮ ⋮

7h 7 GPMC_FCLK cycles

23-21 Reserved 0 Reserved

20-16 ADVWROFFTIME ADV# de-assertion time from start cycle time for write accesses

0 0 GPMC_FCLK cycle

1h 1 GPMC_FCLK cycle

⋮ ⋮

1Fh 31 GPMC_FCLK cycles

15-13 Reserved 0 Reserved

12-8 ADVRDOFFTIME ADV# de-assertion time from start cycle time for read accesses

0 0 GPMC_FCLK cycle

1h 1 GPMC_FCLK cycle

⋮ ⋮

1Fh 31 GPMC_FCLK cycles

7 ADVEXTRADELAY ADV# Add Extra Half GPMC.FCLK cycle

0 ADV Timing control signal is not delayed

1 ADV Timing control signal is delayed of half GPMC_FCLK clock cycle

378

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...