ELM

www.ti.com

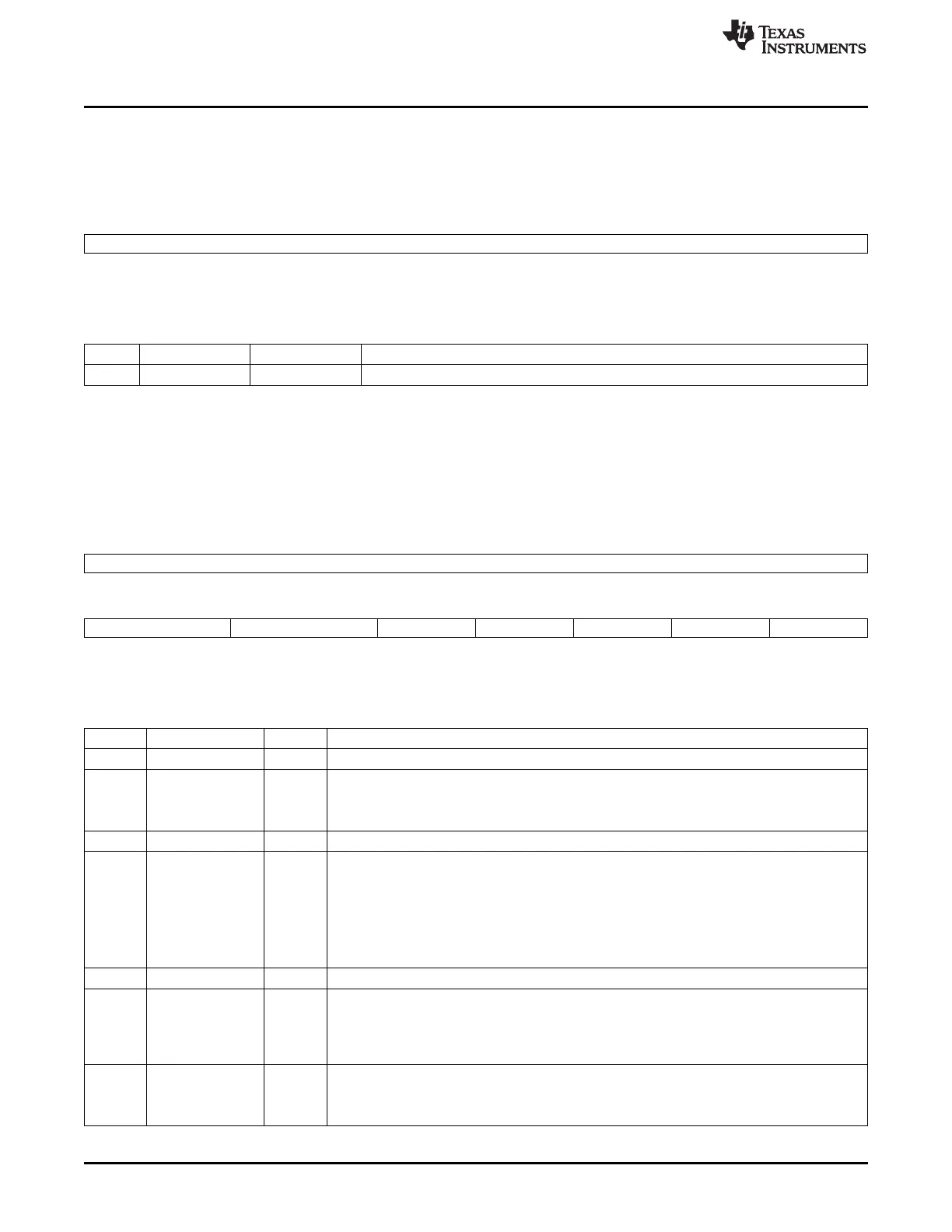

7.4.5.1 ELM Revision Register (ELM_REVISION)

This register contains the IP revision code. The ELM Revision Register (ELM_REVISION) is shown in

Figure 7-141 and described in Table 7-175.

Figure 7-141. ELM Revision Register (ELM_REVISION)

31 0

REVISION

R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-175. ELM Revision Register (ELM_REVISION) Field Descriptions

Bit Field Value Description

31-0 REVISION 0-FFFF FFFFh IP Revision

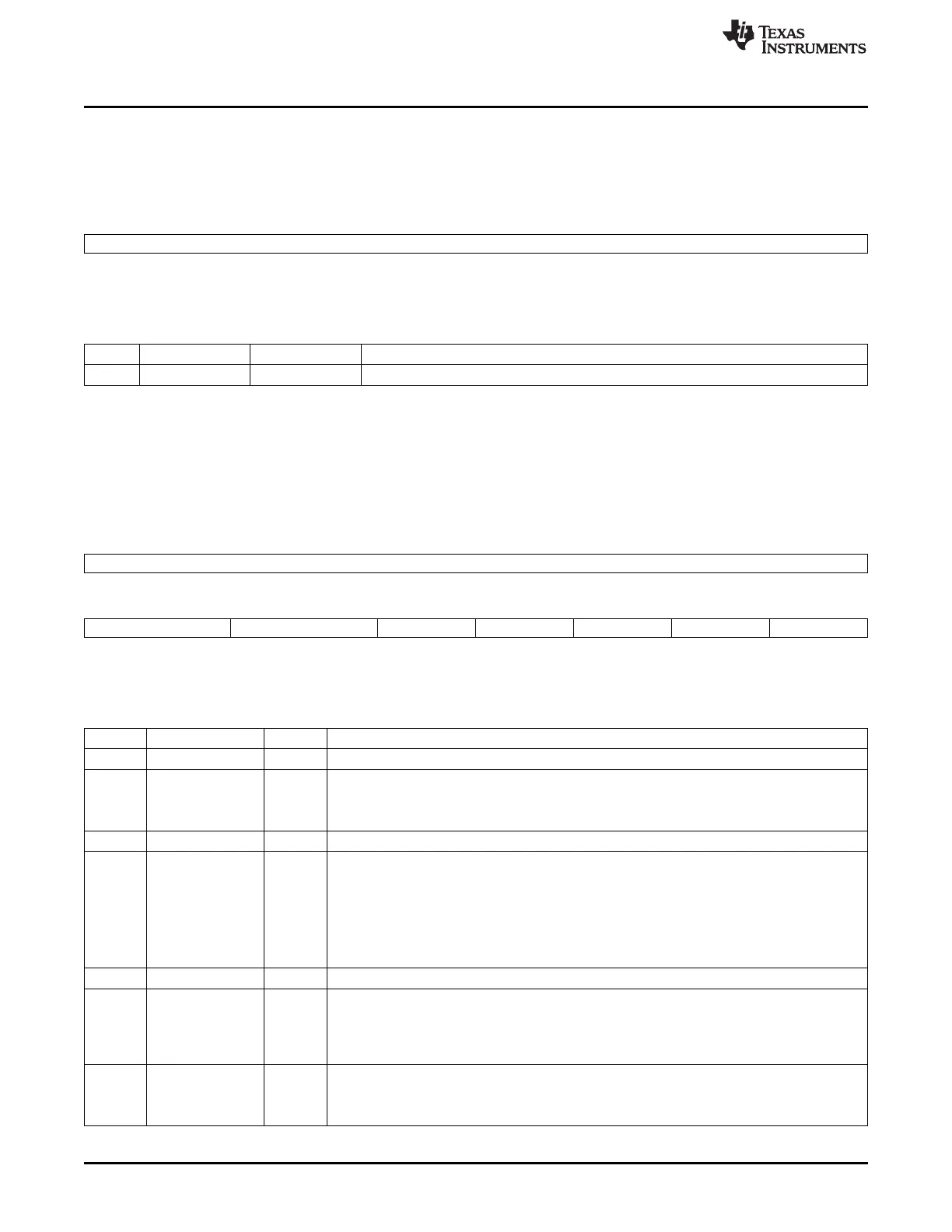

7.4.5.2 ELM System Configuration Register (ELM_SYSCONFIG)

This register allows controlling various parameters of the OCP interface. The ELM System Configuration

Register (ELM_SYSCONFIG) is shown in Figure 7-142 and described in Table 7-176.

Figure 7-142. ELM System Configuration Register (ELM_SYSCONFIG)

31 16

Reserved

R-0

15 9 8 7 5 4 3 2 1 0

Reserved CLOCKACTIVITYOCP Reserved SIDLEMODE Reserved SOFTRESET AUTOGATING

R-0 R/W-0 R-0 R/W-2 R-0 R/W-0 R/W-1

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-176. ELM System Configuration Register (ELM_SYSCONFIG) Field Descriptions

Bit Field Value Description

31-9 Reserved 0 Reserved

8 CLOCKACTIVITY OCP Clock activity when module is in IDLE mode (during wake up mode period).

OCP

0 OCP Clock can be switch-off

1 OCP Clock is maintained during wake up period

7-5 Reserved 0 Reserved

4-3 SIDLEMODE Slave interface power management (IDLE req/ack control).

0 FORCE Idle. IDLE request is acknowledged unconditionally and immediately. (Default Dumb

mode for safety)

1h NO idle. IDLE request is never acknowledged.

2h SMART Idle. The acknowledgment to an IDLE request is given based on the internal activity.

3h Reserved - do not use

2 Reserved 0 Reserved

1 SOFTRESET Module software reset. This bit is automatically reset by hardware (During reads, it always

returns 0.). It has same effect as the OCP hardware reset.

0 Normal mode.

1 Start soft reset sequence.

0 AUTOGATING Internal OCP clock gating strategy. (No module visible impact other than saving power.)

0 OCP clock is free-running.

1 Automatic internal OCP clock gating strategy is applied based on the OCP interface activity.

488

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...