EMAC

Physical

Layer

Device

(PHY)

MDIO

RMII_TXD[1:0]

50 MHz

Transformer

RJ-45

RMII_TXEN

RMII_RMREFCLK

RMII_RXD[1–0]

RMII_CRS_DV

RMII_RXER

MDIO_CLK

MDIO_DATA

www.ti.com

Integration

Table 14-6. GMII Interface Signal Descriptions in MII (100/10Mbps) Mode (continued)

Signal Type Description

The receive data valid signal indicates that the MRXD pins are generating nibble

MRXDV I

data for use by the 3PSW. It is driven synchronously to MRCLK.

Management data clock (MDIO_CLK). The MDIO data clock is sourced by the

MDCLK O MDIO module on the system. It is used to synchronize MDIO data access

operations done on the MDIO pin.

MDIO DATA(MDI0_D). MDIO data pin drives PHY management data into and

out of the PHY by way of an access frame consisting of start of frame, read/write

MDIO I/O

indication,PHY address, register address, and data bit cycles. The MDIO_D pin

acts as an output for all but the data bit cycles at which time it is an input for read

operations.

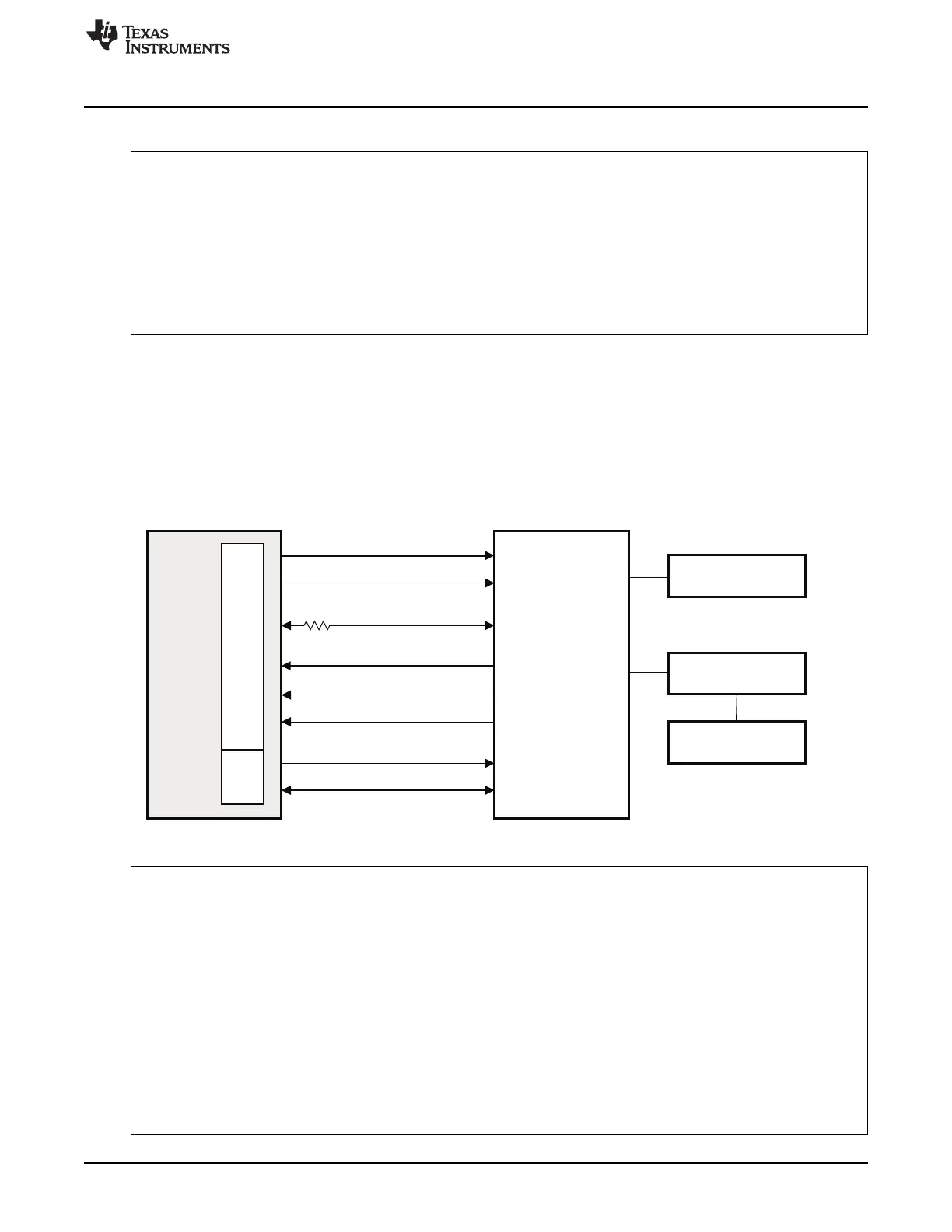

14.2.6 RMII Signal Connections and Descriptions

Figure 14-4 shows a device with integrated 3PSW and MDIO interfaced via a RMII connection in a typical

system.

The individual CPSW and MDIO signals for the RMII interface are summarized in Table 14-7.

For more information, see either the IEEE 802.3 standard or ISO/IEC 8802-3:2000(E).

Figure 14-4. RMII Interface Connections

Table 14-7. RMII Interface Signal Descriptions

Signal Type Description

Transmit data. The transmit data pins are a collection of 2 bits of data.

RMII_TXD[1-0] O RMII_TXD0 is the least-significant bit (LSB). The signals are synchronized by

RMII_REFCLK and valid only when RMII_TXEN is asserted.

Transmit enable. The transmit enable signal indicates that the RMII_TXD pins

RMII_TXEN O are generating data for use by the PHY. RMII_TXEN is synchronous to

RMII_MHZ_50_CLK.

RMII reference clock.

RMII_REFCLK I

The reference clock is used to synchronize all RMII signals. RMII_REFCLK must

be continuous and fixed at 50 MHz.

Receive data. The receive data pins are a collection of 2 bits of data.

RMII_RXD0 is the least-significant bit (LSB). The signals are synchronized by

RMII_RXD[1-0] I

RMII_REFCLK and valid only when RM_CRS_DV is asserted and RMII_RXER is

deasserted.

Carrier sense/receive data valid. Multiplexed signal between carrier sense and

RMII_CRS_DV I

receive data valid.

1173

SPRUH73H–October 2011–Revised April 2013 Ethernet Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...