www.ti.com

Power, Reset, and Clock Management

8.1.12.1.3 CM_PER_L4FW_CLKSTCTRL Register (offset = 8h) [reset = 102h]

CM_PER_L4FW_CLKSTCTRL is shown in Figure 8-25 and described in Table 8-32.

This register enables the domain power state transition. It controls the SW supervised clock domain state

transition between ON-ACTIVE and ON-INACTIVE states. It also hold one status bit per clock input of the

domain.

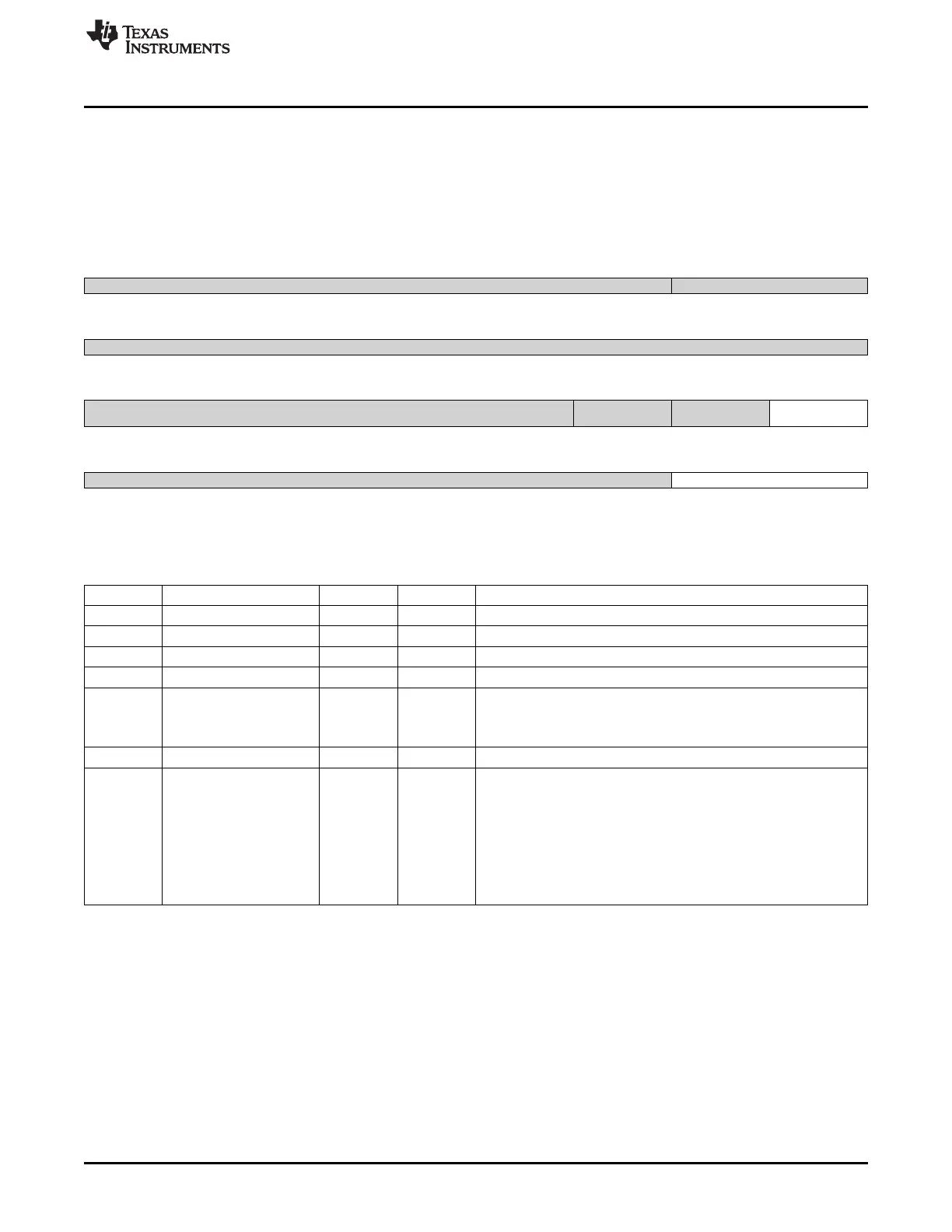

Figure 8-25. CM_PER_L4FW_CLKSTCTRL Register

31 30 29 28 27 26 25 24

Reserved Reserved

R-0h R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved Reserved Reserved CLKACTIVITY_L4FW

_GCLK

R-0h R-0h R-0h R-1h

7 6 5 4 3 2 1 0

Reserved CLKTRCTRL

R-0h R/W-2h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

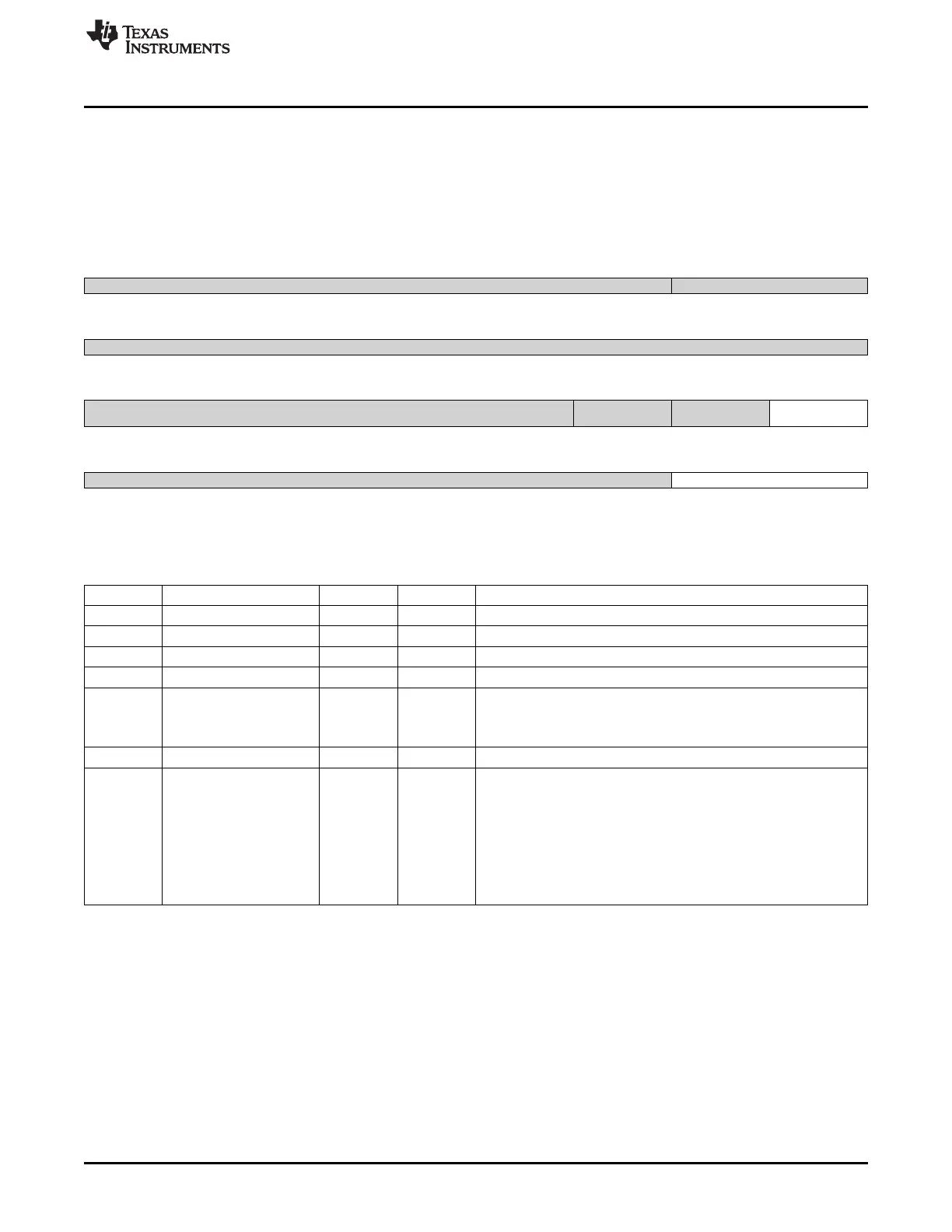

Table 8-32. CM_PER_L4FW_CLKSTCTRL Register Field Descriptions

Bit Field Type Reset Description

31-26 Reserved R 0h

25-11 Reserved R 0h

10 Reserved R 0h

9 Reserved R 0h

8 CLKACTIVITY_L4FW_GC R 1h

This field indicates the state of the L4FW clock in the domain.

LK

0x0 = Inact : Corresponding clock is gated

0x1 = Act : Corresponding clock is active

7-2 Reserved R 0h

1-0 CLKTRCTRL R/W 2h

Controls the clock state transition of the L4 Firewall clock domain.

0x0 = NO_SLEEP : NO_SLEEP: Sleep transition cannot be initiated.

Wakeup transition may however occur.

0x1 = SW_SLEEP : SW_SLEEP: Start a software forced sleep

transition on the domain.

0x2 = SW_WKUP : SW_WKUP: Start a software forced wake-up

transition on the domain.

0x3 = Reserved

553

SPRUH73H–October 2011–Revised April 2013 Power, Reset, and Clock Management (PRCM)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...