www.ti.com

EDMA3 Registers

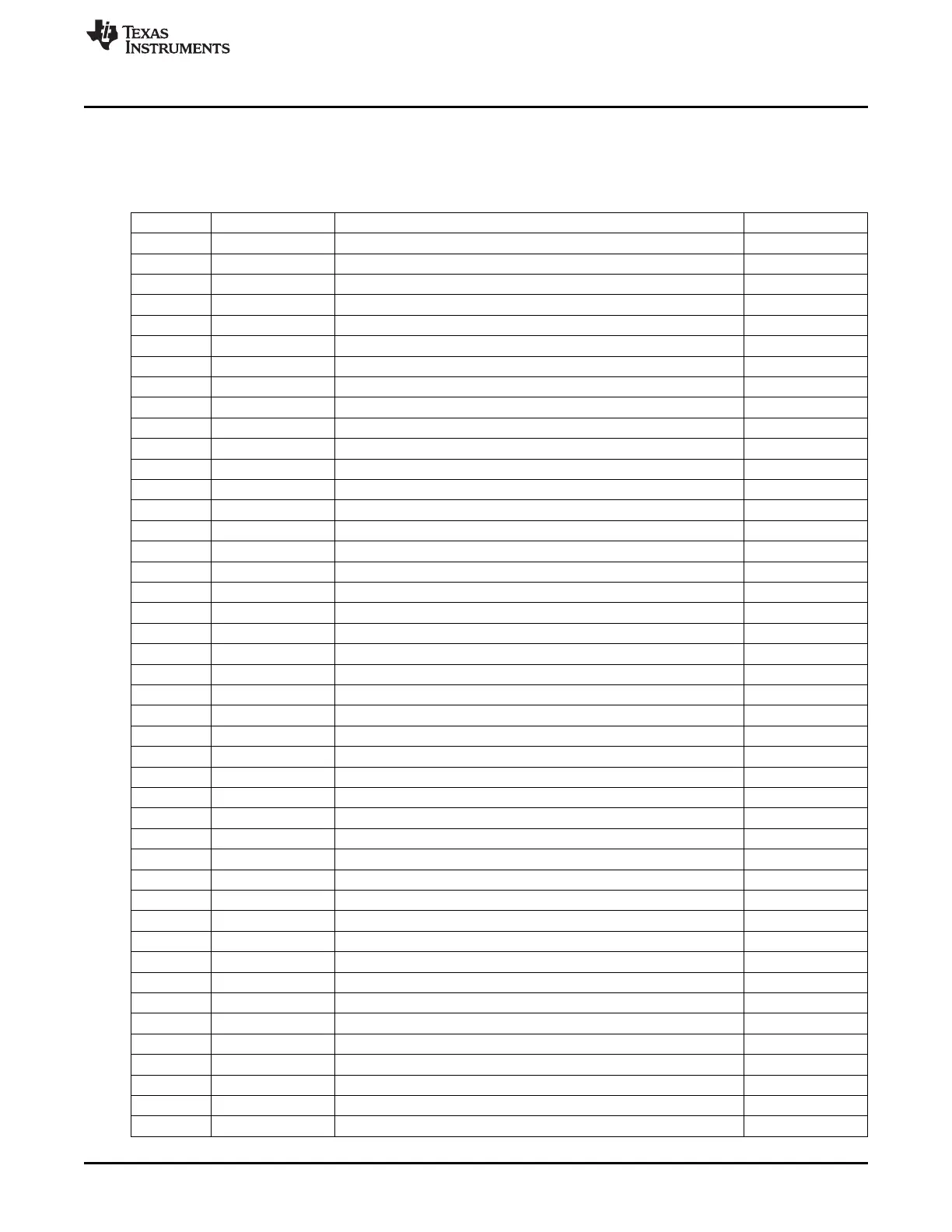

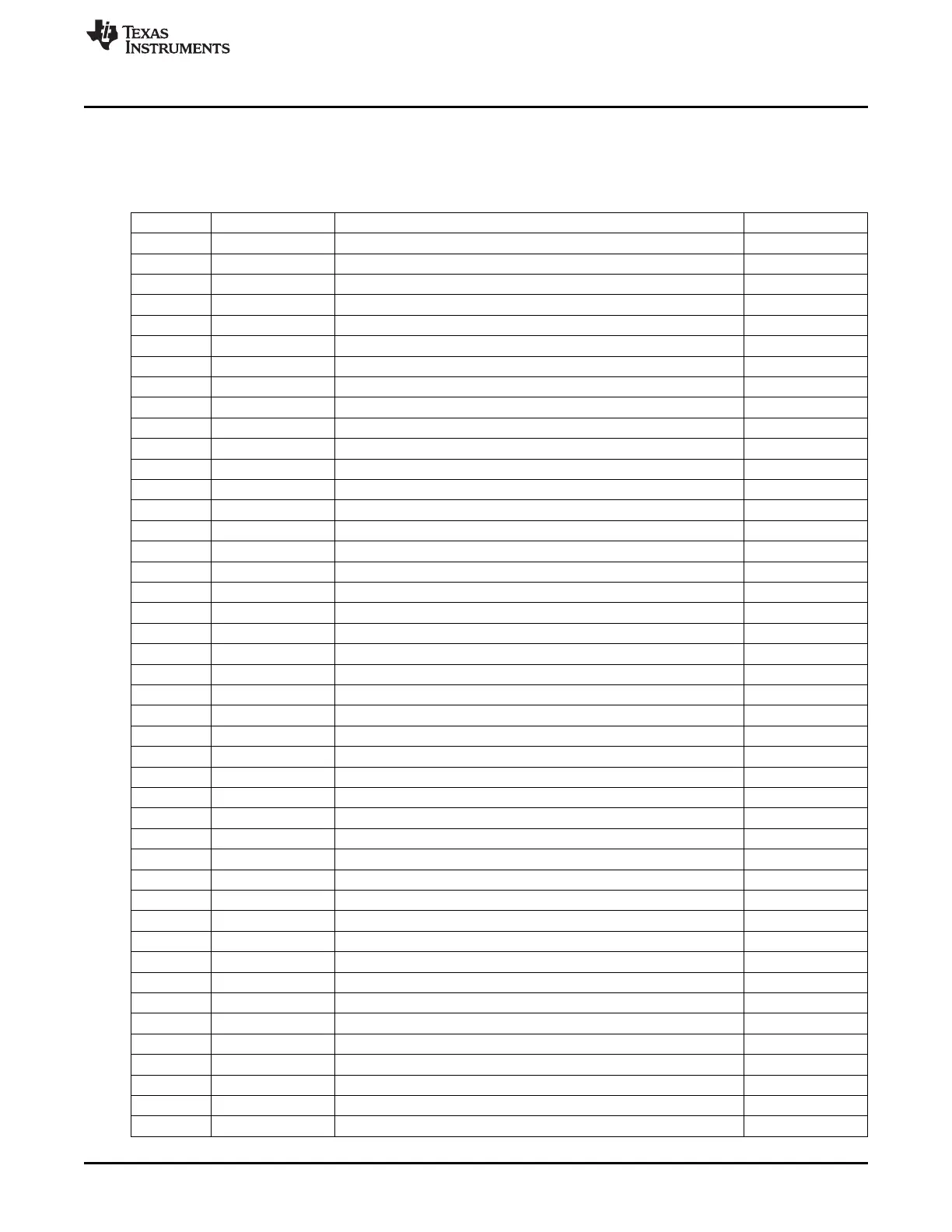

11.4.2 EDMA3 Transfer Controller Registers

Table 11-89 lists the memory-mapped registers for the EDMA3 transfer controller (EDMA3TC).

Table 11-89. EDMA3TC Registers

Offset Acronym Register Description Section

00h PID Peripheral Identification Register Section 11.4.2.1

04h TCCFG EDMA3TC Configuration Register Section 11.4.2.2

10h SYSCONFIG EDMA3TC System Configuration Register Section 11.4.2.3

0100h TCSTAT EDMA3TC Channel Status Register Section 11.4.2.4

0120h ERRSTAT Error Register Section 11.4.2.5.1

0124h ERREN Error Enable Register Section 11.4.2.5.2

0128h ERRCLR Error Clear Register Section 11.4.2.5.3

012Ch ERRDET Error Details Register Section 11.4.2.5.4

0130h ERRCMD Error Interrupt Command Register Section 11.4.2.5.5

0140h RDRATE Read Rate Register Section 11.4.2.6

0240h SAOPT Source Active Options Register Section 11.4.2.7.1

0244h SASRC Source Active Source Address Register Section 11.4.2.7.2

0248h SACNT Source Active Count Register Section 11.4.2.7.3

024Ch SADST Source Active Destination Address Register Section 11.4.2.7.4

0250h SABIDX Source Active Source B-Index Register Section 11.4.2.7.5

0254h SAMPPRXY Source Active Memory Protection Proxy Register Section 11.4.2.7.6

0258h SACNTRLD Source Active Count Reload Register Section 11.4.2.7.7

025Ch SASRCBREF Source Active Source Address B-Reference Register Section 11.4.2.7.8

0260h SADSTBREF Source Active Destination Address B-Reference Register Section 11.4.2.7.9

0280h DFCNTRLD Destination FIFO Set Count Reload Section 11.4.2.7.16

0284h DFSRCBREF Destination FIFO Set Destination Address B Reference Register Section 11.4.2.7.17

0288h DFDSTBREF Destination FIFO Set Destination Address B Reference Register Section 11.4.2.7.18

0300h DFOPT0 Destination FIFO Options Register 0 Section 11.4.2.7.10

0304h DFSRC0 Destination FIFO Source Address Register 0 Section 11.4.2.7.11

0308h DFCNT0 Destination FIFO Count Register 0 Section 11.4.2.7.12

030Ch DFDST0 Destination FIFO Destination Address Register 0 Section 11.4.2.7.13

0310h DFBIDX0 Destination FIFO BIDX Register 0 Section 11.4.2.7.14

0314h DFMPPRXY0 Destination FIFO Memory Protection Proxy Register 0 Section 11.4.2.7.15

0340h DFOPT1 Destination FIFO Options Register 1 Section 11.4.2.7.10

0344h DFSRC1 Destination FIFO Source Address Register 1 Section 11.4.2.7.11

0348h DFCNT1 Destination FIFO Count Register 1 Section 11.4.2.7.12

034Ch DFDST1 Destination FIFO Destination Address Register 1 Section 11.4.2.7.13

0350h DFBIDX1 Destination FIFO BIDX Register 1 Section 11.4.2.7.14

0354h DFMPPRXY1 Destination FIFO Memory Protection Proxy Register 1 Section 11.4.2.7.15

0380h DFOPT2 Destination FIFO Options Register 2 Section 11.4.2.7.10

0384h DFSRC2 Destination FIFO Source Address Register 2 Section 11.4.2.7.11

0388h DFCNT2 Destination FIFO Count Register 2 Section 11.4.2.7.12

038Ch DFDST2 Destination FIFO Destination Address Register 2 Section 11.4.2.7.13

0390h DFBIDX2 Destination FIFO BIDX Register 2 Section 11.4.2.7.14

0394h DFMPPRXY2 Destination FIFO Memory Protection Proxy Register 2 Section 11.4.2.7.15

03C0h DFOPT3 Destination FIFO Options Register 3 Section 11.4.2.7.10

03C4h DFSRC3 Destination FIFO Source Address Register 3 Section 11.4.2.7.11

03C8h DFCNT3 Destination FIFO Count Register 3 Section 11.4.2.7.12

03CCh DFDST3 Destination FIFO Destination Address Register 3 Section 11.4.2.7.13

993

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...