www.ti.com

McSPI Registers

24.4.1.15 McSPI DMA Address Aligned FIFO Receiver Register (MCSPI_DAFRX)

The McSPI DMA address aligned FIFO receiver register (MCSPI_DAFRX) contains the SPI words to

received on the serial link when FIFO used and DMA address is aligned on 256 bit. This register is an

image of one of MCSPI_RX(i) register corresponding to the channel which have its FIFO enabled. The

MCSPI_DAFRX register is shown in Figure 24-40 and described in Table 24-26.

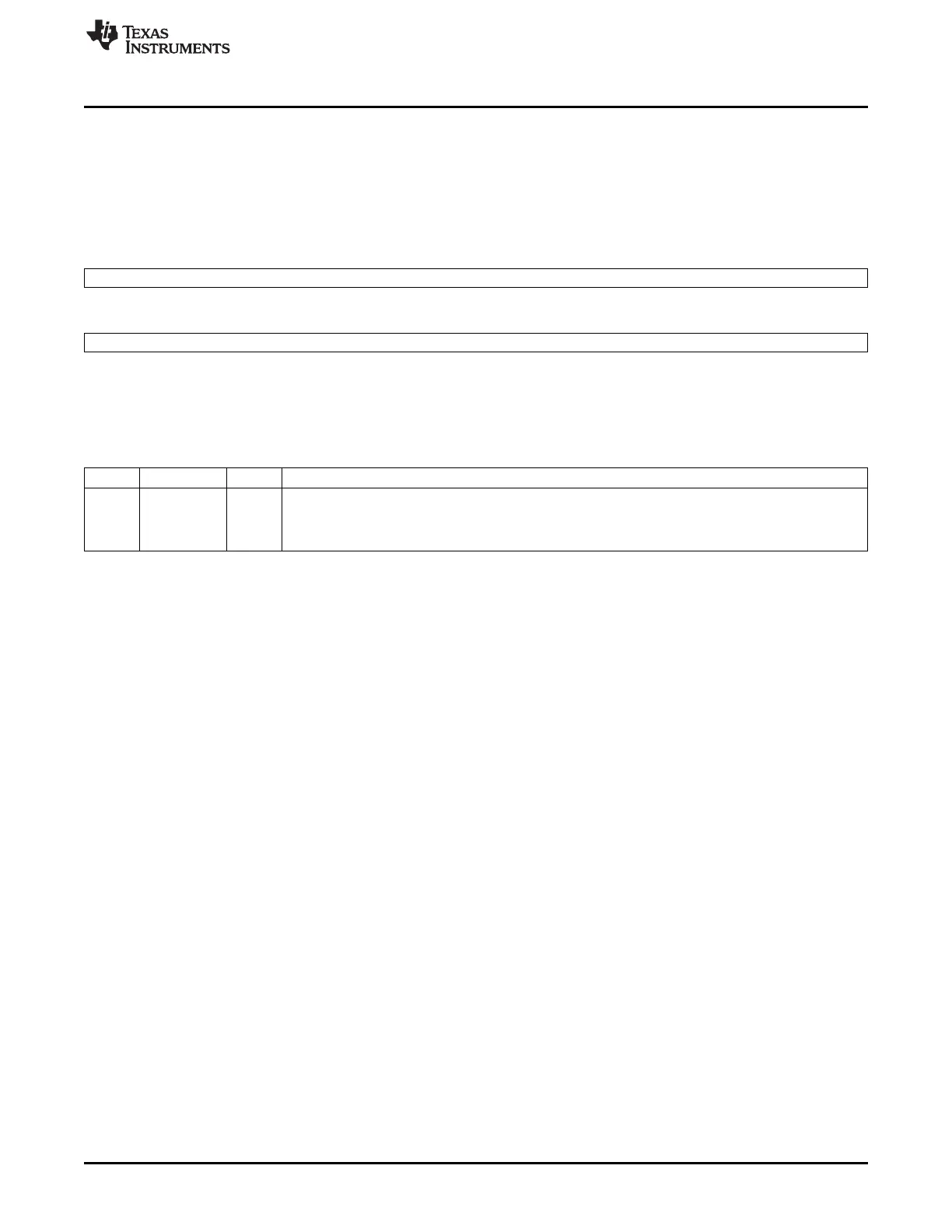

Figure 24-40. McSPI DMA Address Aligned FIFO Receiver Register (MCSPI_DAFRX)

31 16

DAFRDATA

R-0

15 0

DAFRDATA

R-0

LEGEND: R/W = Read/Write; -n = value after reset

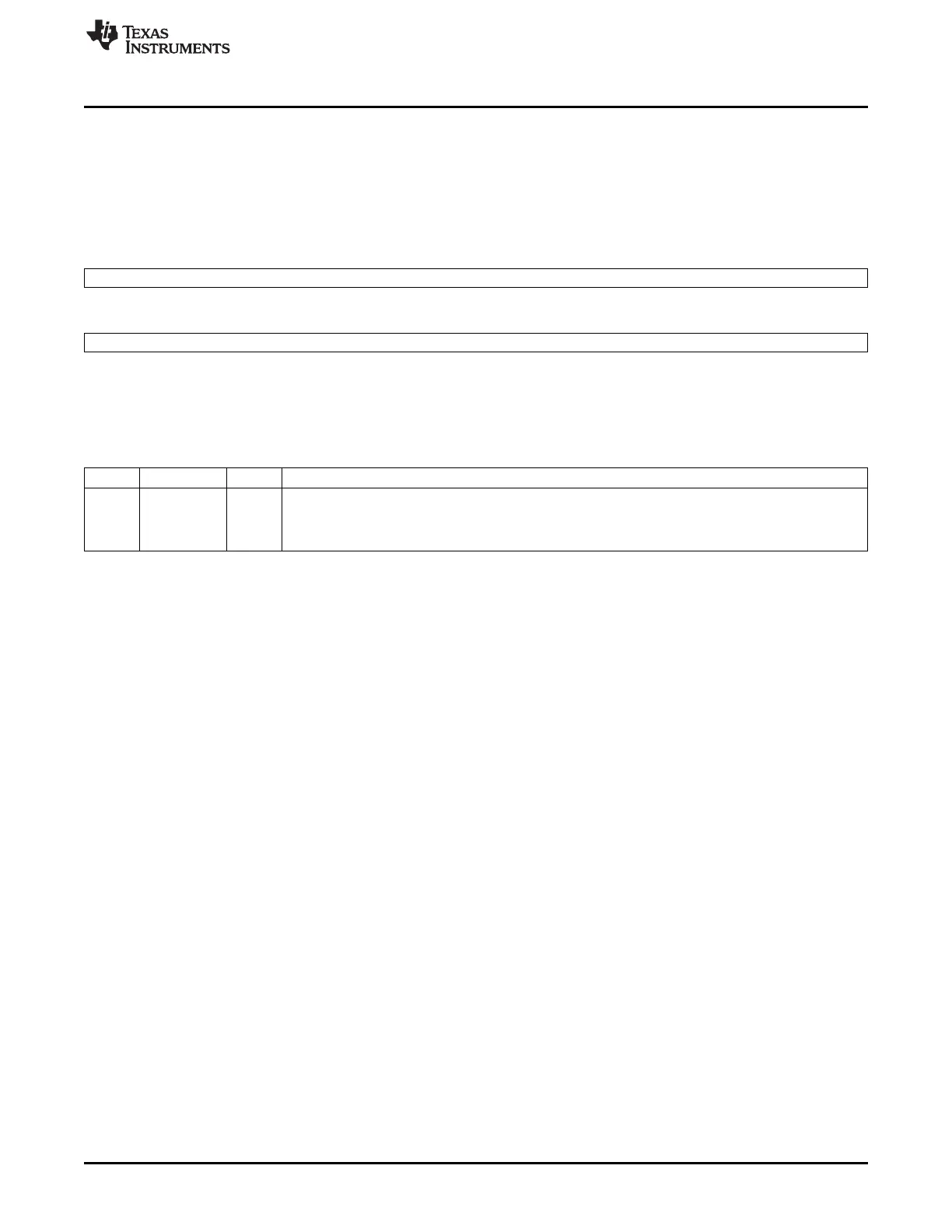

Table 24-26. McSPI DMA Address Aligned FIFO Receiver Register (MCSPI_DAFRX) Field

Descriptions

Bit Field Value Description

31-0 DAFRDATA FIFO Received Data with DMA 256 bit aligned address.

This register is used only when MCSPI_MODULCTRL[FDAA] is set to ‘1’, and only one of the

MCSPI_CH(i)CONF[FFER] of enabled channels is set. Without these conditions, any access to this

register will return a null value.

4055

SPRUH73H–October 2011–Revised April 2013 Multichannel Serial Port Interface (McSPI)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...