www.ti.com

Ethernet Subsystem Registers

14.5.2.44 RX2_FREEBUFFER Register (offset = E8h) [reset = 0h]

RX2_FREEBUFFER is shown in Figure 14-72 and described in Table 14-83.

CPDMA_INT RECEIVE FREE BUFFER REGISTER CHANNEL 2

Figure 14-72. RX2_FREEBUFFER Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

RX_FREEBUFFER

W-0h

7 6 5 4 3 2 1 0

RX_FREEBUFFER

W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

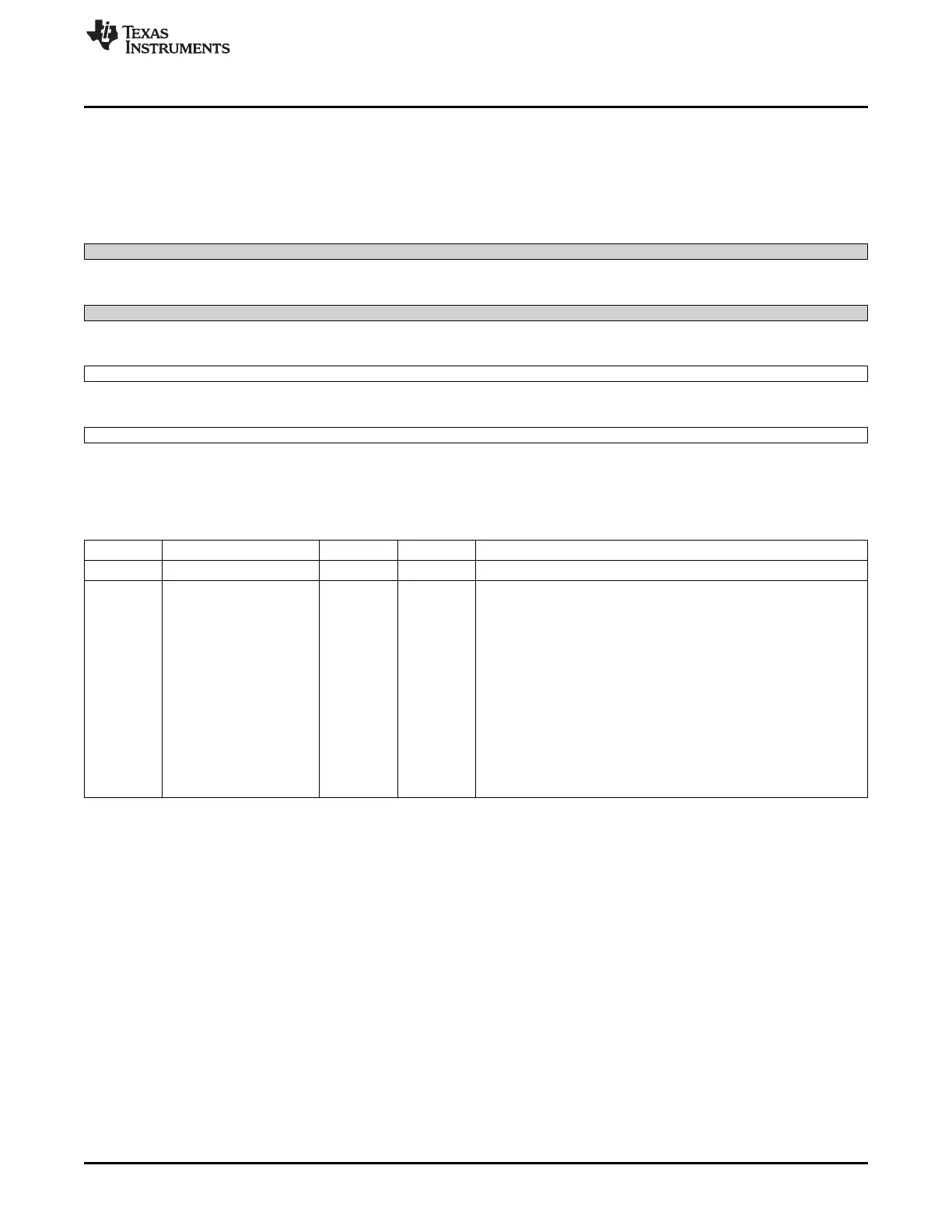

Table 14-83. RX2_FREEBUFFER Register Field Descriptions

Bit Field Type Reset Description

31-16 Reserved R 0h

15-0 RX_FREEBUFFER W 0h Rx Free Buffer Count - This field contains the count of free buffers

available.

The rx_pendthresh value is compared with this field to determine if

the receive threshold pending interrupt should be asseted (if

enabled).

This is a write to increment field.

This field rolls over to zero on overflow.

If receive threshold pending interrupts are used, the host must

initialize this field to the number of available buffers (one register per

channel).

The port decrements (by the number of buffers in the received

frame) the associated channel register for each received frame.

This is a write to increment field.

The host must write this field with the number of buffers that have

been freed due to host processing.

1303

SPRUH73H–October 2011–Revised April 2013 Ethernet Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...