www.ti.com

UART Registers

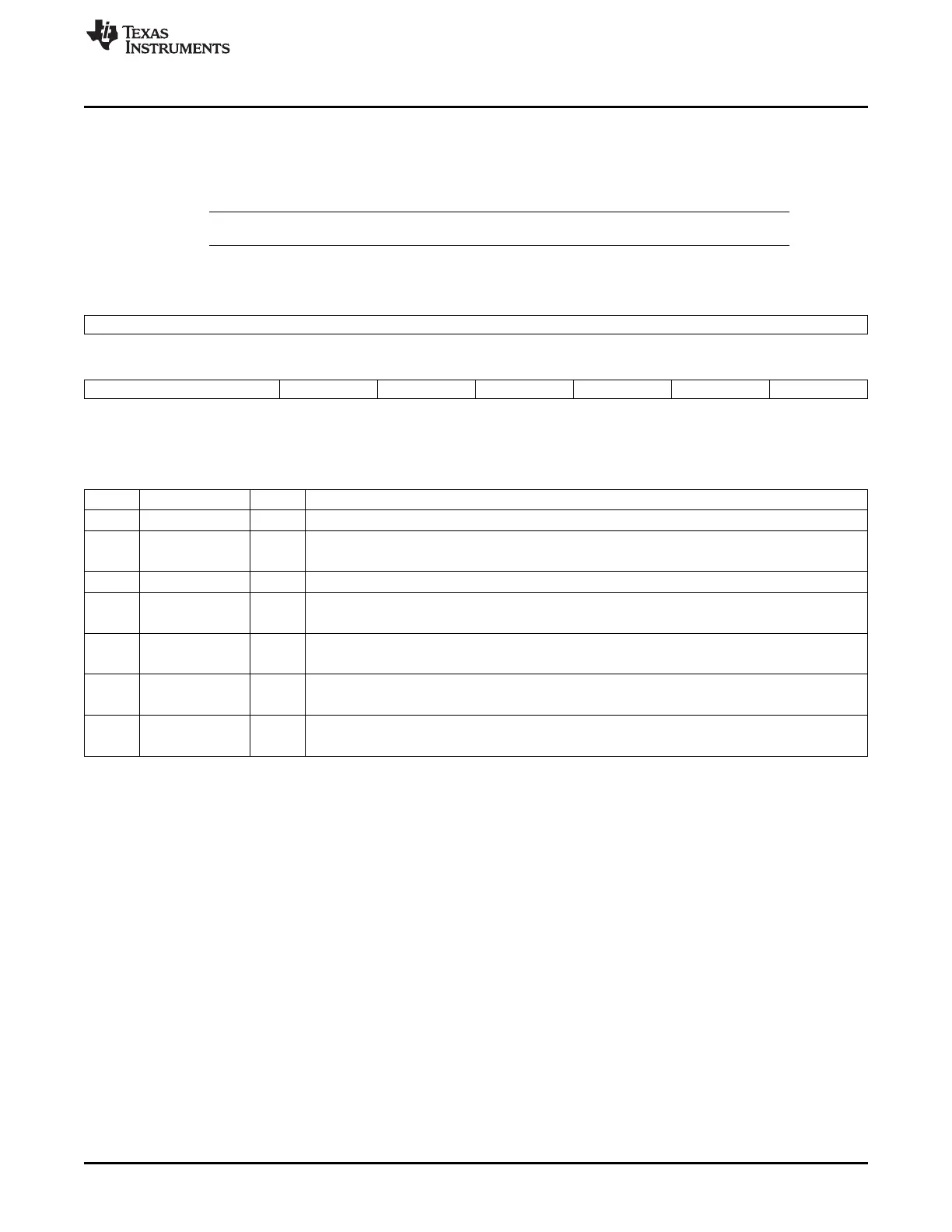

19.5.1.8 Interrupt Identification Register (IIR) - CIR Mode

The CIR interrupt identification register (IIR) is a read-only register that provides the source of the

interrupt. The CIR interrupt identification register (IIR) is shown in Figure 19-41 and described in Table 19-

37.

NOTE: An interrupt source can be flagged only if enabled in the IER register.

Figure 19-41. CIR Interrupt Identification Register (IIR)

15 8

Reserved

R-0

7 6 5 4 3 2 1 0

Reserved TXSTATUSIT Reserved RXOEIT RXSTOPIT THRIT RHRIT

R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

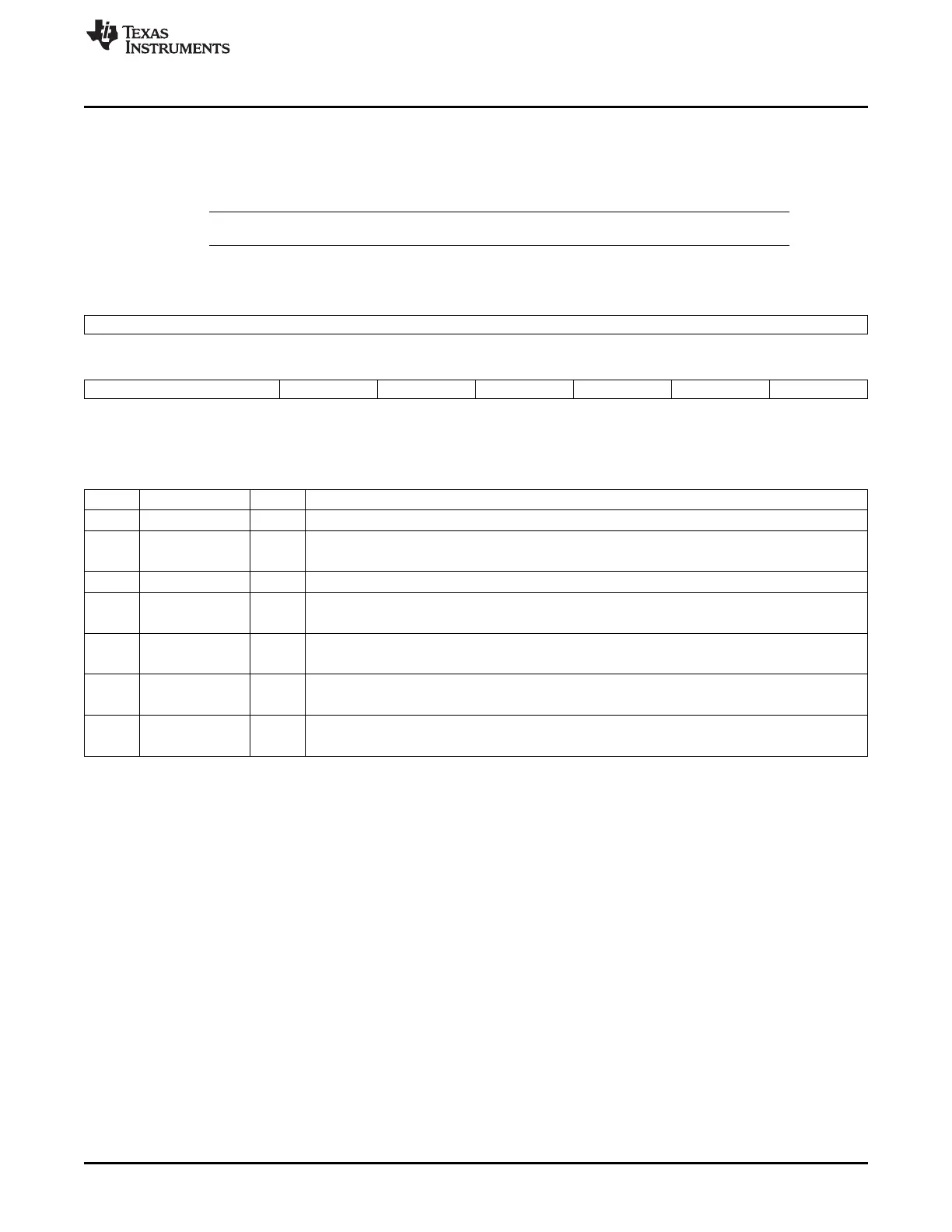

Table 19-37. CIR Interrupt Identification Register (IIR) Field Descriptions

Bit Field Value Description

15-6 Reserved 0 Reserved.

5 TXSTATUSIT 0 TX status interrupt inactive

1 TX status interrupt active

4 Reserved 0 Reserved.

3 RXOEIT 0 RX overrun interrupt inactive

1 RX overrun interrupt active

2 RXSTOPIT 0 Receive stop interrupt is inactive

1 Receive stop interrupt is active

1 THRIT 0 THR interrupt inactive

1 THR interrupt active

0 RHRIT 0 RHR interrupt inactive

1 RHR interrupt active

3513

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...