www.ti.com

Functional Description

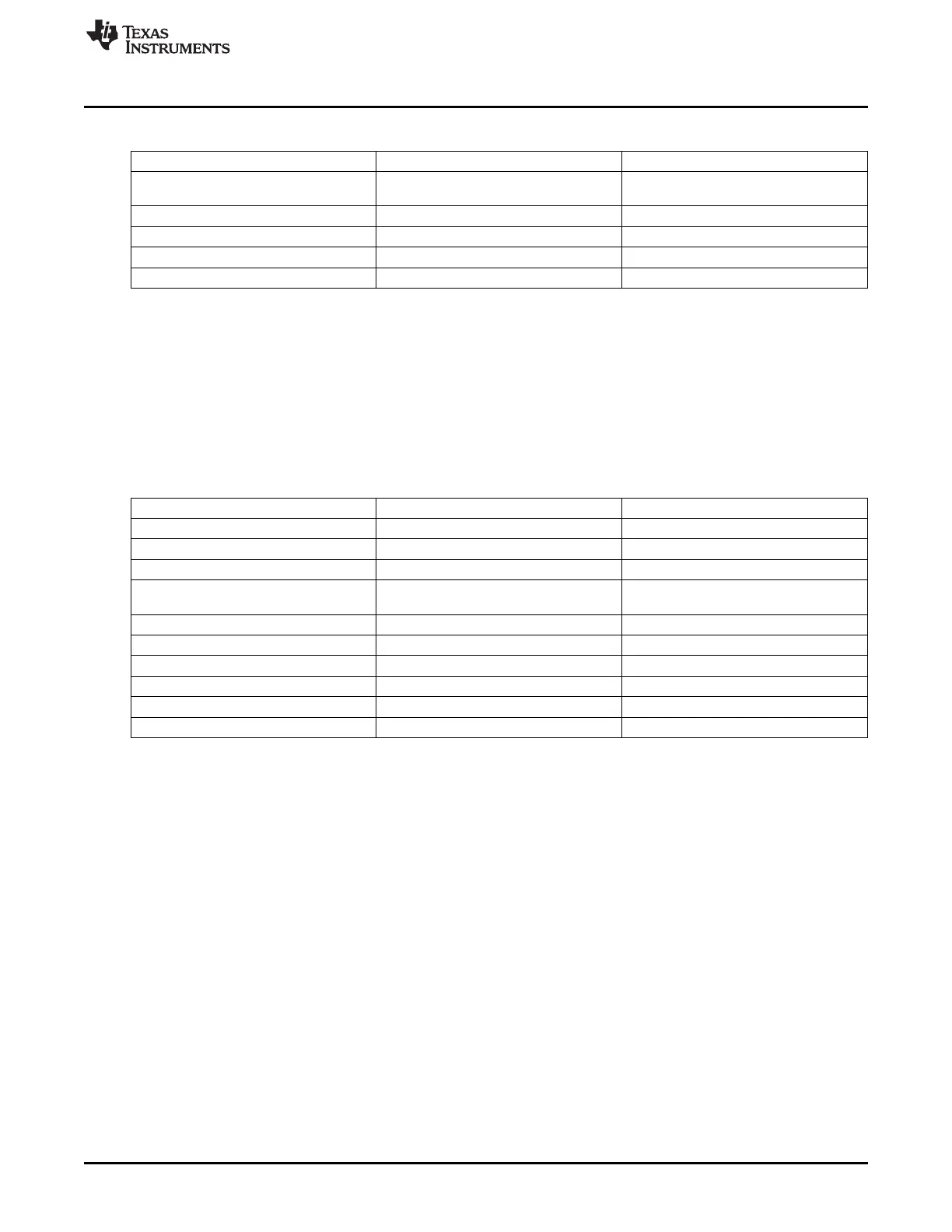

Table 26-3. RAM Exception Vectors (continued)

Address Exception Content

Address of default pre-fetch abort

4030CE2Ch Pre-fetch abort

handler

(1)

4030CE30h Data abort Address of default data abort handler

(1)

4030CE34h Unused 20090h

4030CE38h IRQ Address of default IRQ handler

4030CE3Ch FIQ 20098h

(1)

The default handlers for pre-fetch and data abort are performing reads from CP15 debug registers to retrieve the reason of the

abort:

• In case of pre-fetch abort: the IFAR register is read from CP15 and stored into R0. The IFSR register is read and stored into

the R1 register. Then the ROM Code jumps to the pre-fetch abort dead loop (20088h).

• In case of data abort: the DFAR register is read from CP15 and stored into R0. The DFSR register is read and stored into

the R1 register. Then the ROM Code jumps to the data abort dead loop (2008Ch).

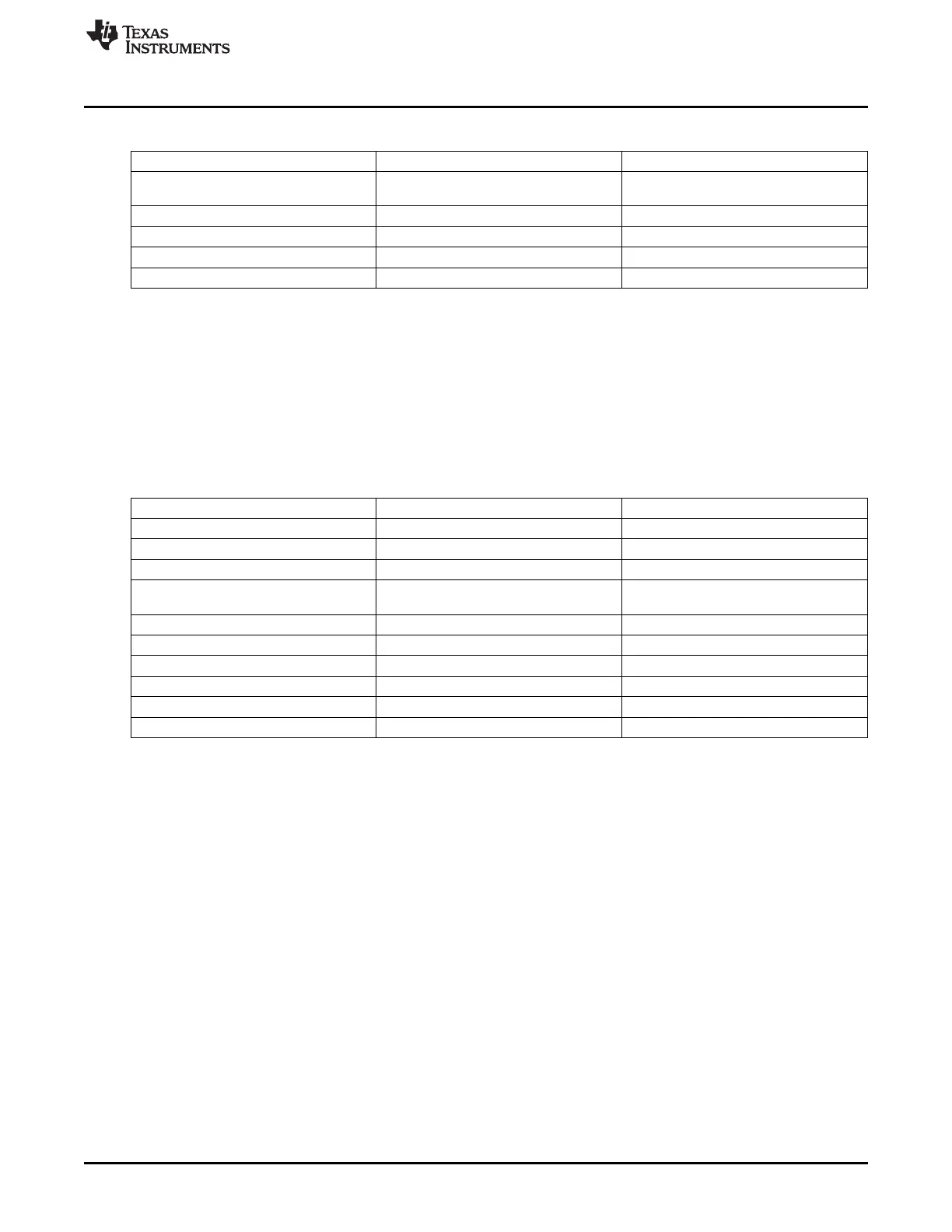

Tracing Data

This area contains trace vectors reflecting the execution path of the public boot. Section 26.1.12 describes

the usage of the different trace vectors and lists all the possible trace codes.

Table 26-4. Tracing Data

Address Size[bytes] Description

4030CE40h 4 Current tracing vector, word 1

4030CE44h 4 Current tracing vector, word 2

4030CE48h 4 Current tracing vector, word 3

Current copy of the PRM_RSTST register

4030CE4Ch 4

(reset reasons)

4030CE50h 4 Cold reset run tracing vector, word 1

4030CE54h 4 Cold reset run tracing vector, word 2

4030CE58h 4 Cold reset run tracing vector, word 3

4030CE5Ch 4 Reserved

4030CE60h 4 Reserved

4030CE64h 4 Reserved

Static Variables

This area contains the ROM Code static variables used during boot time.

26.1.4 Start-up and Configuration

26.1.4.1 ROM Code Start-up

The Public ROM Code is physically located at the address 20000h.

4101

SPRUH73H–October 2011–Revised April 2013 Initialization

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...